Clock regeneration delay chain with high precision and low kickback noise

A delay chain, high-precision technology, used in clocks, time-to-digital converters, devices for measuring time intervals, etc. Phase interval consistency, guaranteed duty cycle consistency, and improved anti-noise performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

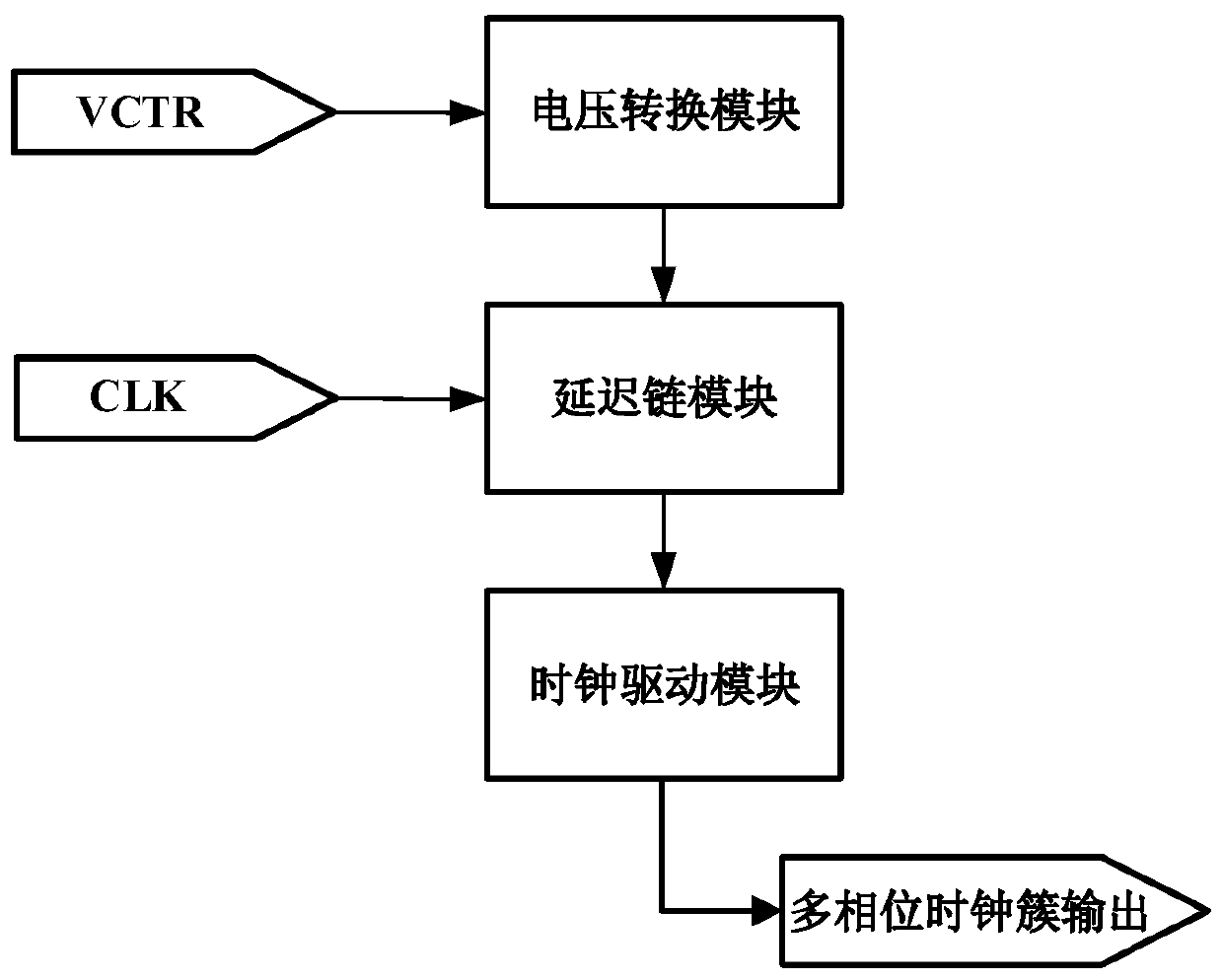

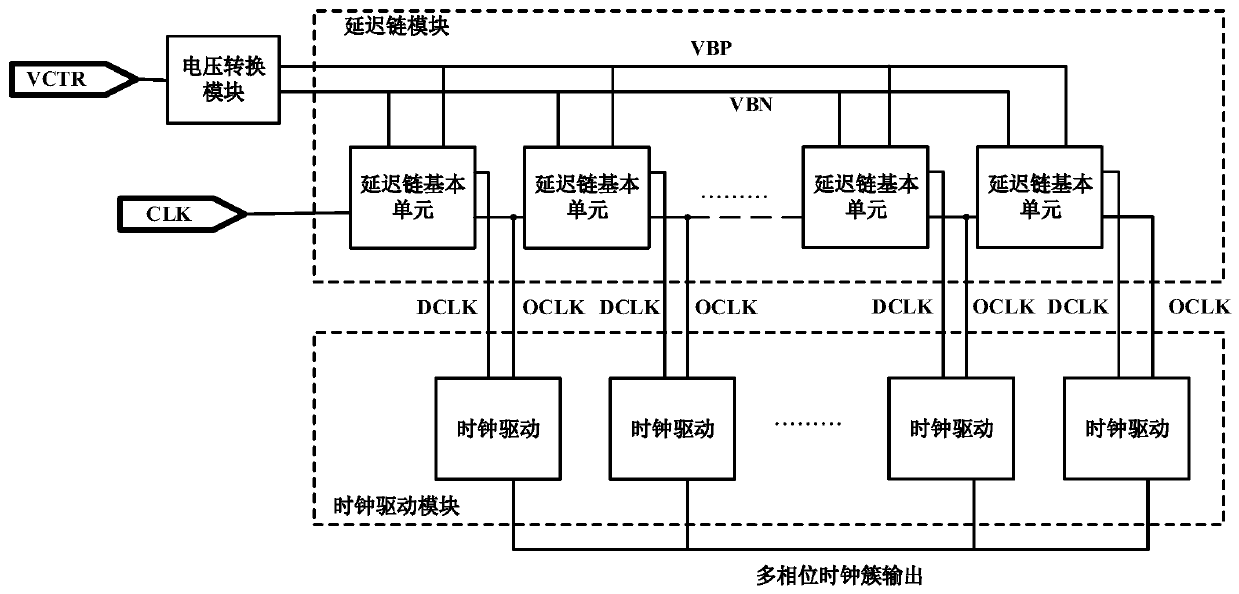

[0050] See figure 1 , figure 1 It is a schematic structural diagram of a clock regeneration delay chain with high precision and low kickback noise provided by an embodiment of the present invention, including:

[0051] A voltage conversion module, connected to the voltage input terminal, for converting the input signal into a first voltage signal and a second voltage signal;

[0052]A delay chain module, connected to the voltage conversion module and a clock input terminal, for controlling the clock delay time according to the first voltage signal and the second voltage signal to obtain a first clock signal cluster and a second clock signal cluster;

[0053] A clock driving module, connected to the delay chain module, is used for receiving and processing the first clock signal cluster and the second clock signal cluster, and outputting a multi-phase clock signal cluster.

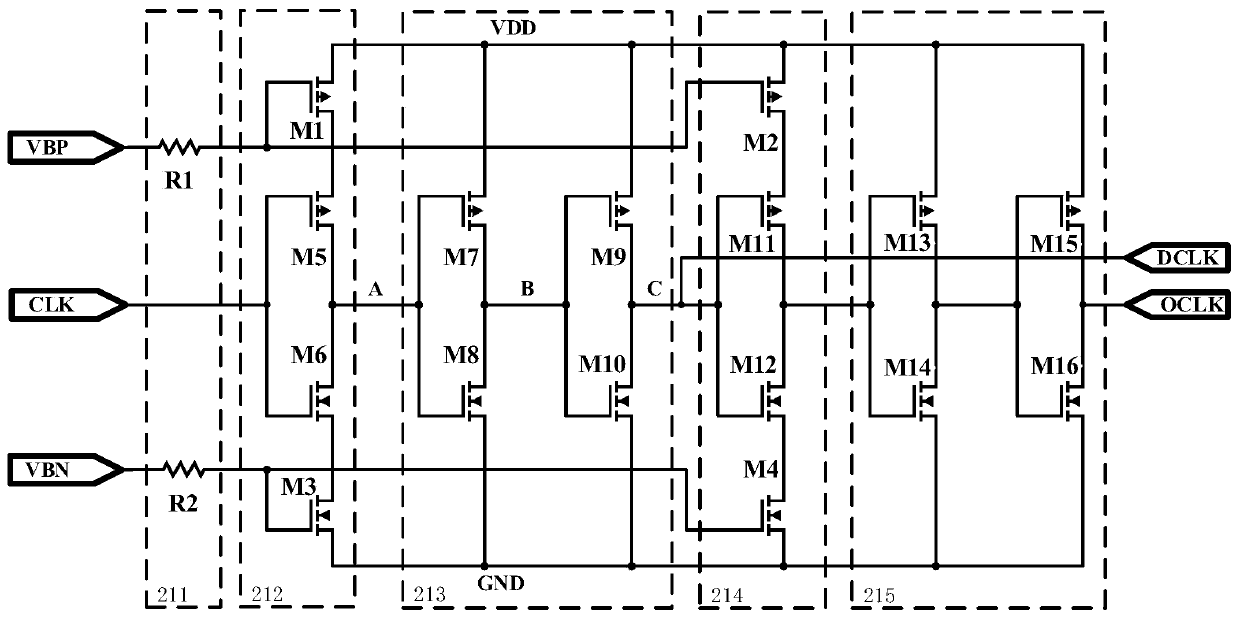

[0054] In this embodiment, the voltage input signal VCTR is connected to the input terminal of the volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More