Method for Biasing Outputs of a Folded Cascode Stage in a Comparator and Corresponding Comparator

A folded cascode, comparator technology, applied in amplifiers with semiconductor devices/discharge tubes, multiple input and output pulse circuits, amplifiers, etc. Output speed, effect of increasing travel time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

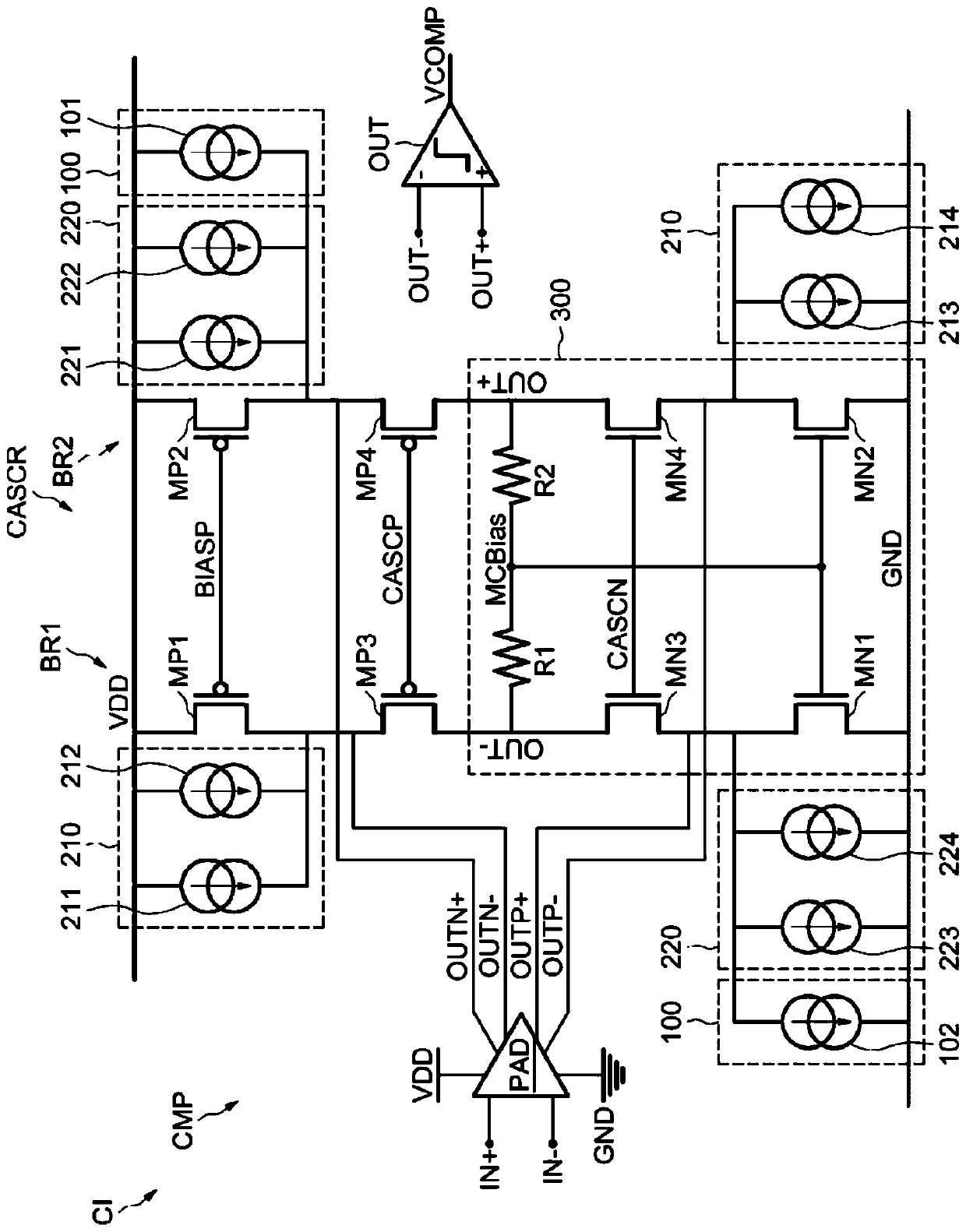

[0036] figure 2 An exemplary integrated circuit CI is shown, which includes a comparator CMP configured to generate a voltage at a first voltage level (logic '1') when the level of the positive input voltage IN+ exceeds the level of the negative input voltage IN-. ) signal VCOMP.

[0037] The comparator CMP comprises a differential preamplification stage PAD receiving positive and negative input voltages on respective inputs IN+, IN- (referred to as positive and negative inputs, respectively).

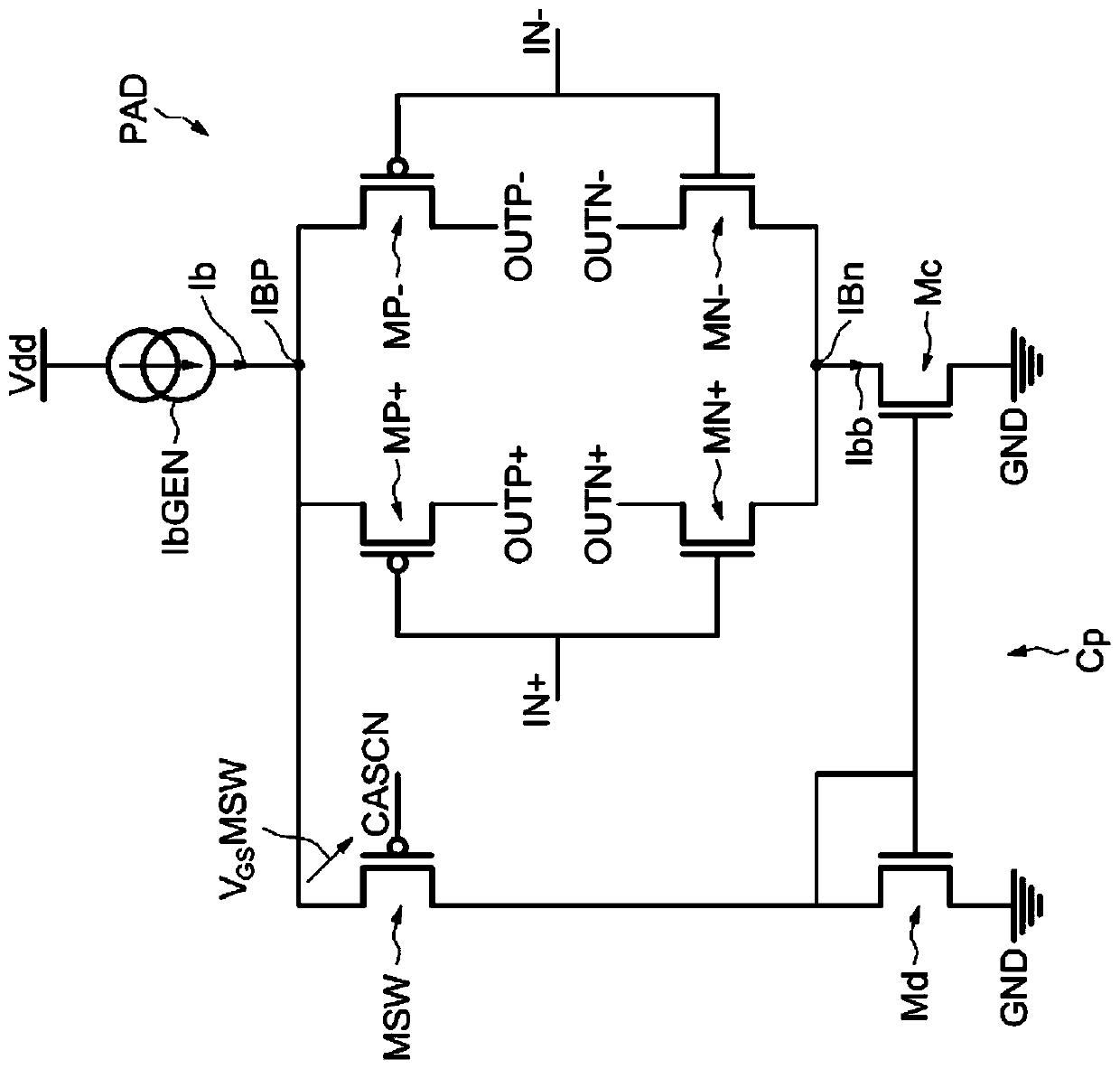

[0038] image 3 An example of a differential preamplification stage PAD and a power supply device configured to provide a bias current Ib to the stage PAD is shown.

[0039] The differential preamplifier stage PAD includes two pairs of differential transistors. One differential pair, called a p-type conduction differential pair, includes two PMOS transistors MP+, MP- whose sources are coupled to a p-type conduction bias node IBP. Another differential pair, called an n-type conduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More