Chip packaging structure and packaging method

A chip packaging structure and chip packaging technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of different packaging structures and packaging processes, inability to meet, small application range, etc., to achieve good overall performance and extended coupling resistance. effect of value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

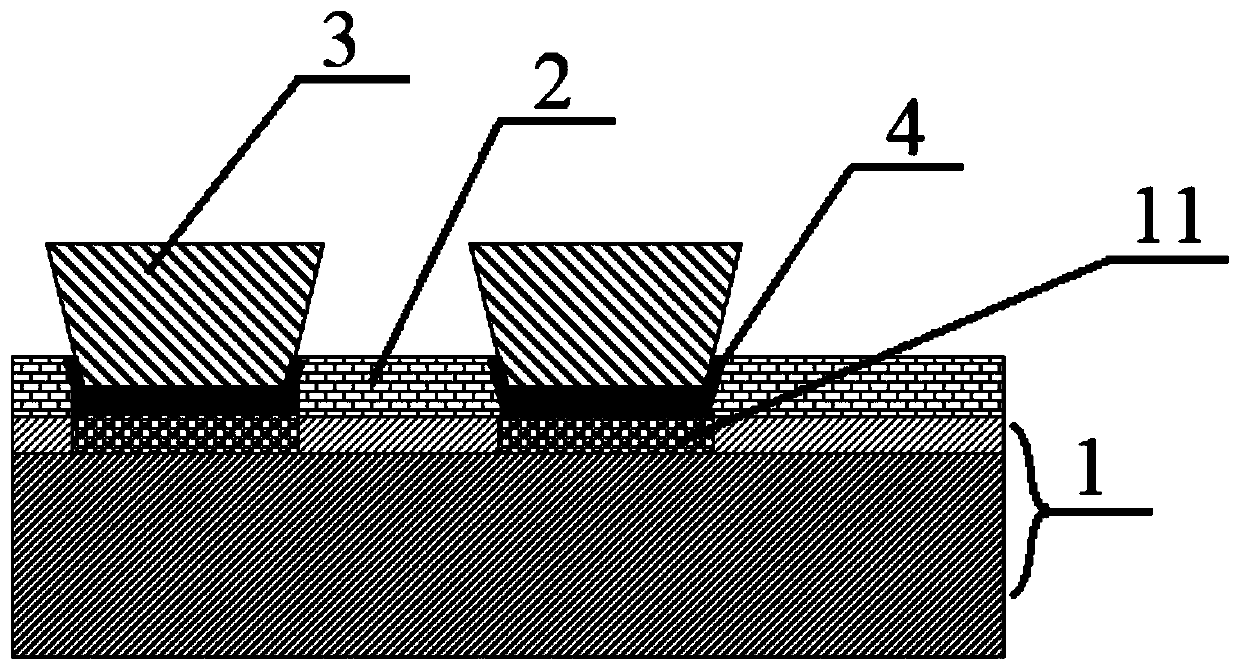

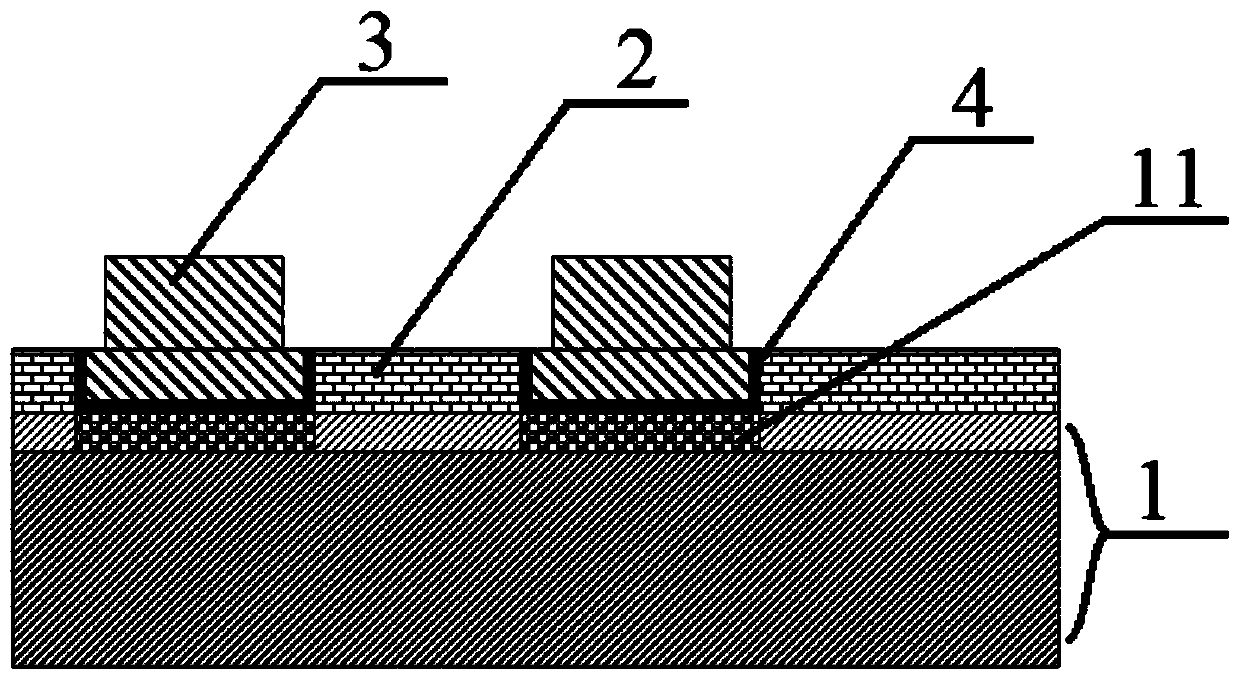

[0039] This embodiment provides a fan-out chip packaging structure, such as figure 1 As shown, the package structure includes: a chip to be packaged, a silicon-based dielectric layer and an extension pad.

[0040] Among them, the chip to be packaged has multiple pads ( figure 1 Although only two pads are shown in FIG. 1, those skilled in the art should understand that there are multiple pads for the chip to be packaged).

[0041] Such as figure 1 As shown, the silicon-based dielectric layer 2 is provided on the device surface of the chip to be packaged 1, and a first groove 21 corresponding to the pad 11 of the chip to be packaged 1 is opened in the silicon-based dielectric layer 2, and the pad 11 passes through The first groove 21 is exposed outside the silicon-based dielectric layer 2. Here, the device surface of the chip to be packaged 1 immediately refers to the surface where the pad 11 of the chip to be packaged 1 is located. The silicon-based dielectric layer 2 is a thin film...

Embodiment 2

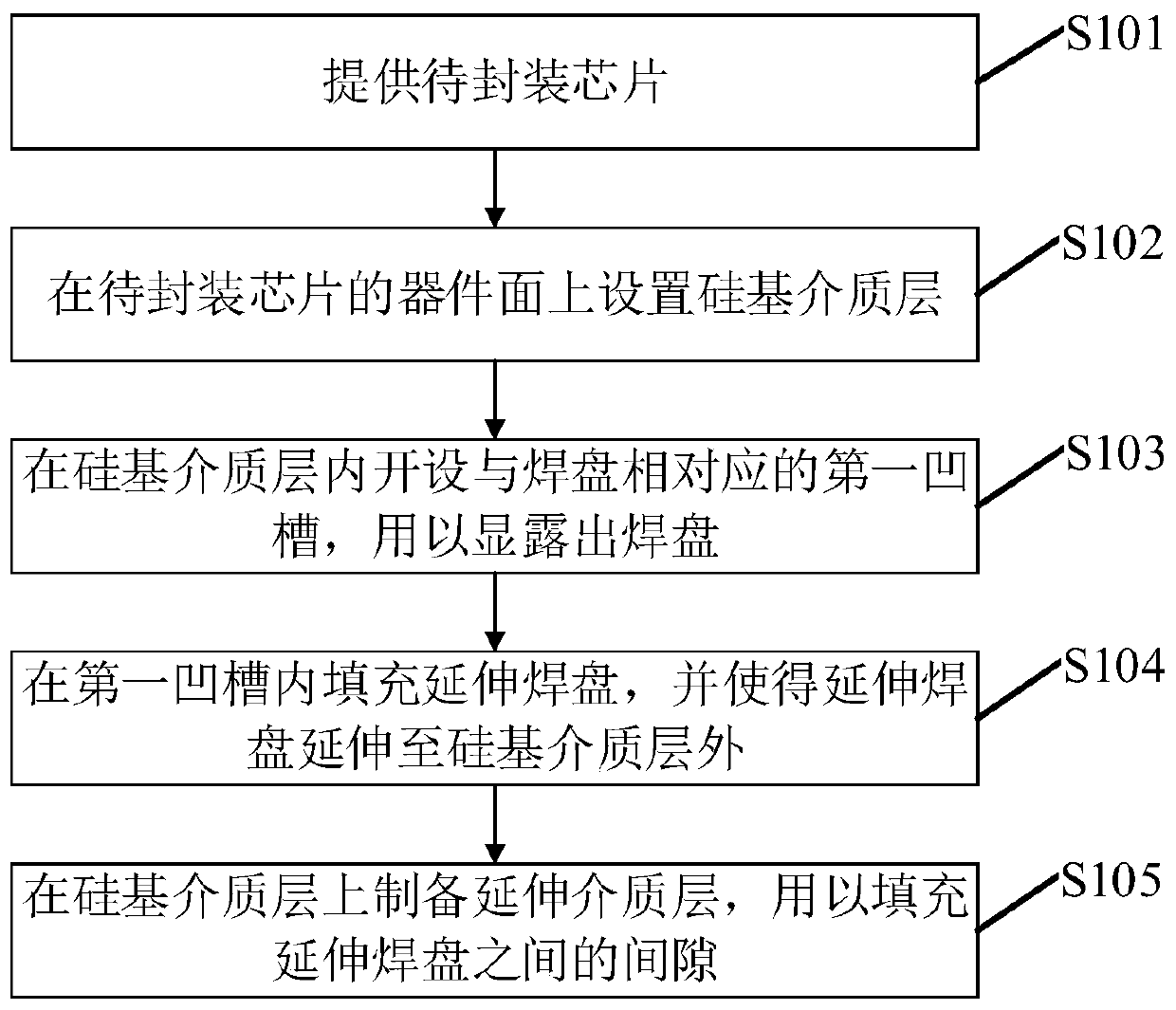

[0053] This embodiment provides a chip packaging method, and the packaging structure in Example 1 can be prepared according to this method and its preferred embodiments, and what has been described will not be repeated.

[0054] The chip packaging method provided in this embodiment, such as image 3 As shown, including the following steps:

[0055] S101: Provide chip 1 to be packaged. Here, the chip 1 to be packaged has multiple pads 11, Figure 4 Although only one pad 11 is shown in the figure, those skilled in the art should understand that there are multiple pads 11 of the chip 1 to be packaged.

[0056] S102: A silicon-based dielectric layer 2 is provided on the device surface of the chip 1 to be packaged. Such as Figure 4 As shown, a silicon-based dielectric layer 2 is provided on the device surface of the chip 1 to be packaged. The silicon-based dielectric layer 2 is a thin film layer that completely covers the device surface. Its thickness is usually several to tens of micro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com