Three-dimensional heterogeneous integrated chip and preparation method thereof

An integrated chip and chip technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of new memory application difficulties, computing system speed and safety limitations, etc., and achieve fast data exchange speed, increased difficulty, wire parasitic The effect of low capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

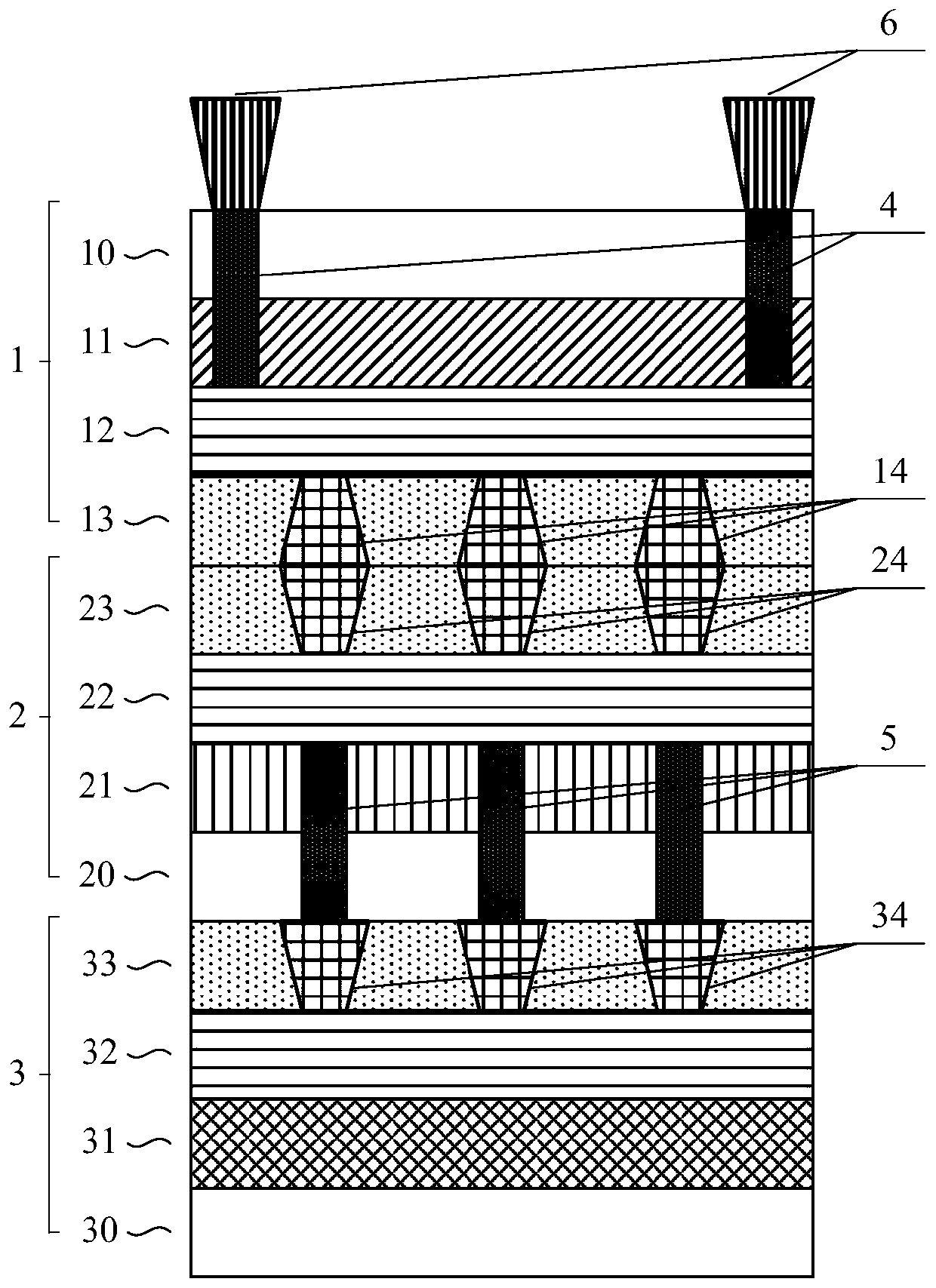

[0052] The technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Apparently, the described embodiments are only some of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of this application.

[0053] Reference herein to "one embodiment" or "an embodiment" refers to a specific feature, structure or characteristic that may be included in at least one implementation of the present application. In the description of the embodiments of the present application, it should be understood that the orientations or positional relationships indicated by the terms "upper", "lower", "top", and "bottom" are based on the orientations or positional relationships shown in the drawing...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More