Interface type IP system application verification platform and verification method

A system application and verification platform technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of low flexibility of simulation model, difficult programming of simulation model, poor portability of driver code, etc., to improve verification. Efficiency and verification quality, reduce the workload of writing and debugging, and facilitate the effect of testing abnormal scenarios

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] This embodiment relates to the verification technology of Intellectual Property (IP) in System on a Chip (SOC), Application Specific Integrated Circuit (ASIC), Field Programmable GataArray (FPGA). The field, especially related to the system application verification method and verification platform of the controller interface (master interface) IP and the device interface (slave interface) IP in the interface IP.

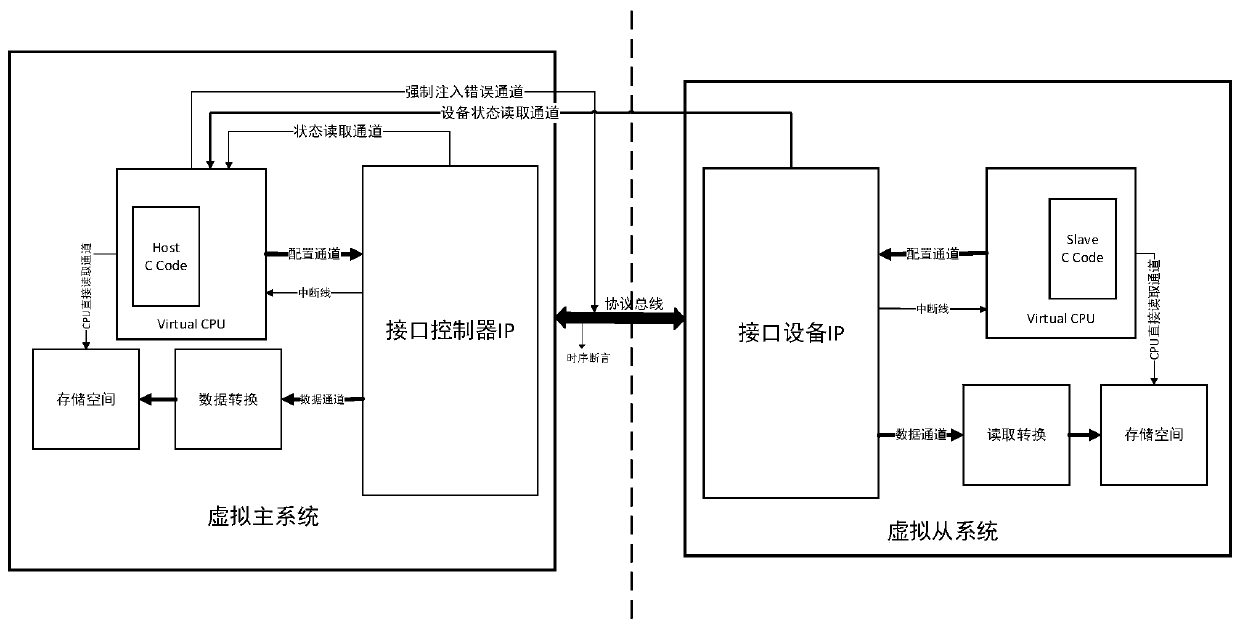

[0041] Such as figure 1 As shown, this embodiment integrates the controller interface IP and the device interface IP, and is divided into two virtual independent systems: a virtual master system and a virtual slave system. Among them, Host is the main interface or controller interface; Host C Code is the controller driver code; Slave C Code is the device driver code; Virtual CPU is the virtual CPU, which can absorb the CPU driver code and convert it into register configuration commands through the configuration channel Operate, and can execute the interrupt hand...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More