Digital phase-locked loop frequency synthesizer

A frequency synthesizer, digital phase-locked loop technology, applied in the direction of automatic power control, electrical components, etc., can solve the disadvantages of digital phase-locked loop frequency synthesizer low power consumption and low-cost integration, large chip area, large power consumption Consumption and other issues to achieve the effect of saving area and power consumption, simplifying circuit design, and speeding up the loop locking process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described below in conjunction with specific embodiment:

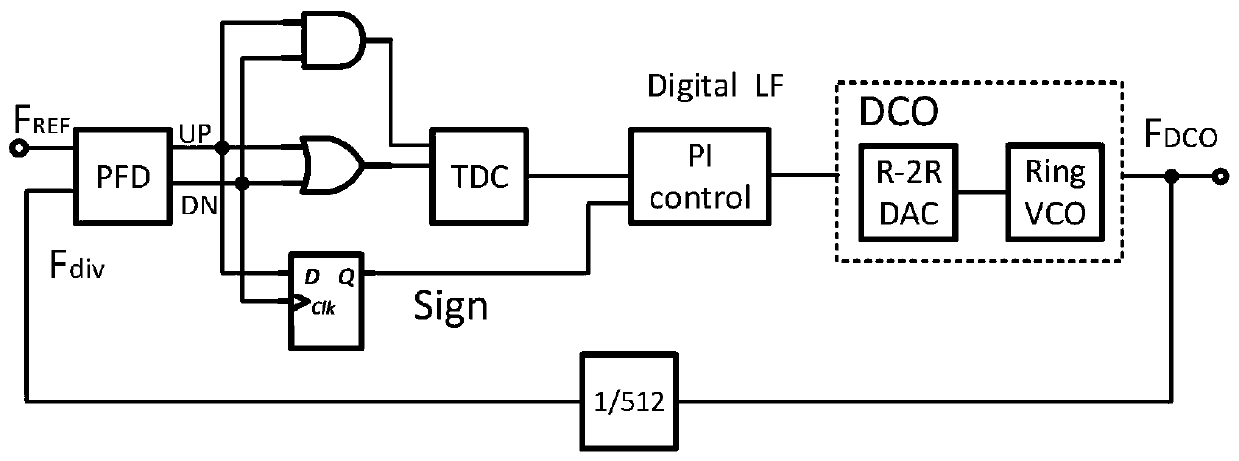

[0023] Take the design of a digital PLL frequency synthesizer with input 32.768kHz and output 16MHz as an example.

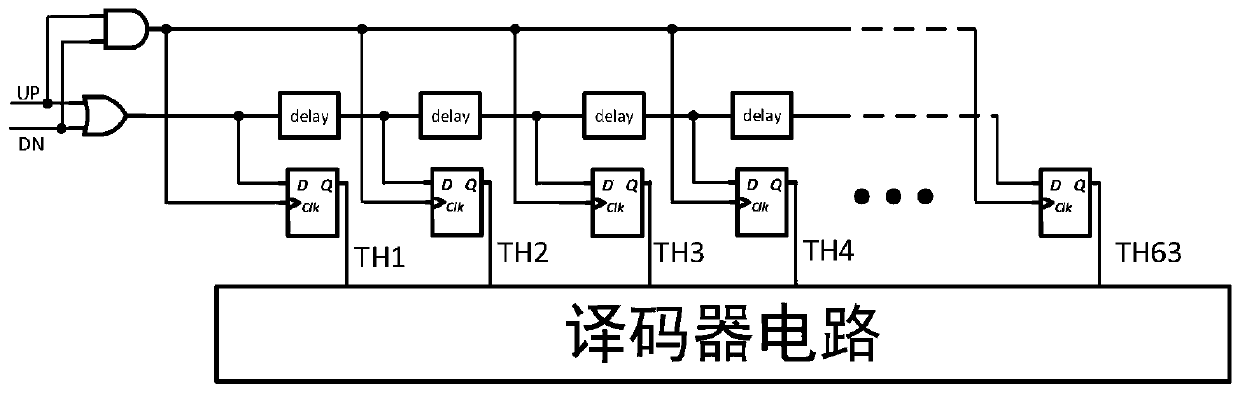

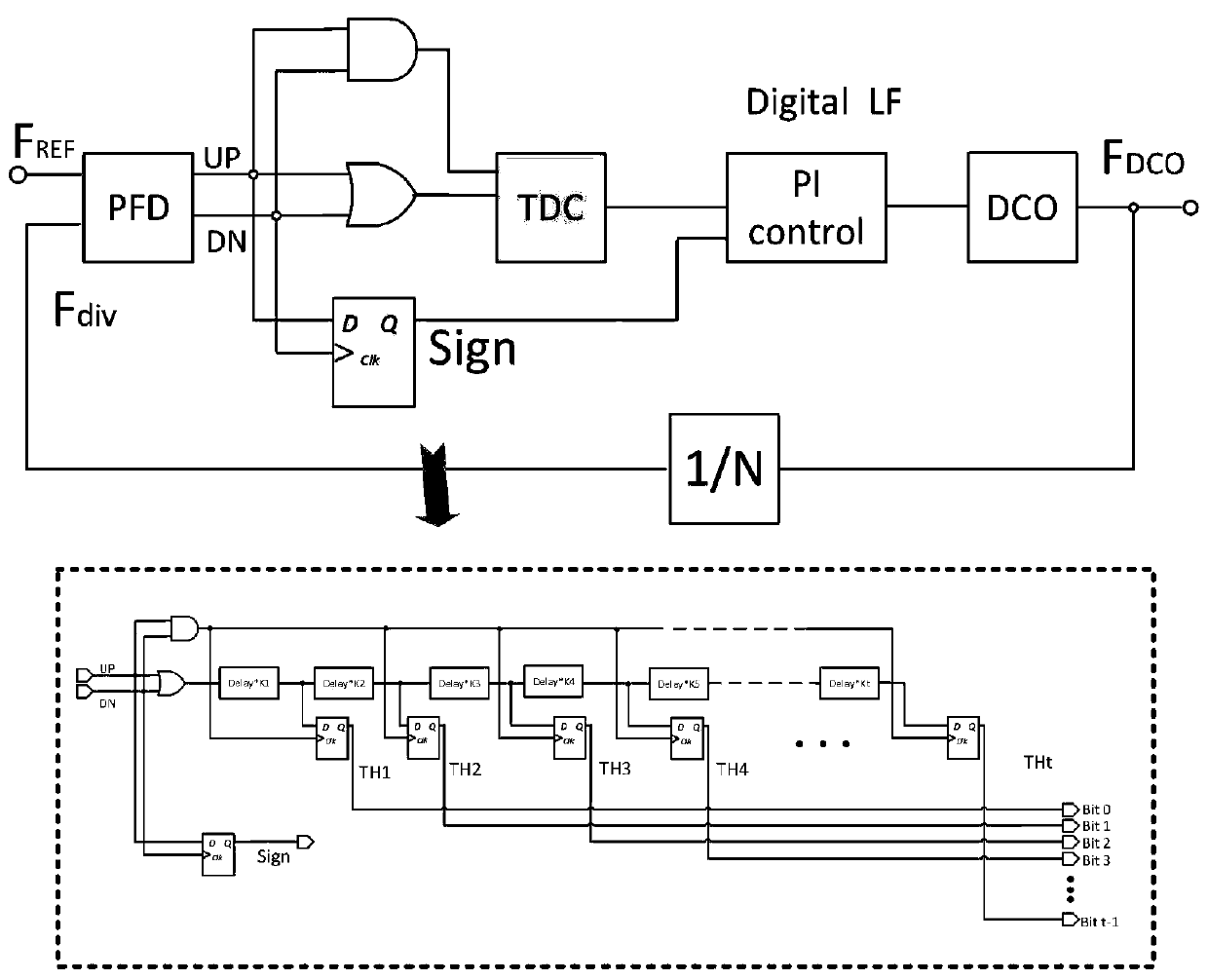

[0024] (1) System structure design

[0025] Due to the need to achieve fixed frequency synthesis from 32kHz to 16MHz, the frequency division ratio N is set to 512, and the system block diagram is as follows image 3 shown. PFD will input reference frequency signal F REF and frequency divider output frequency signal F div The phase difference of the signal is converted into UP and DN signals, and then the UP and DN signals are processed by the gate circuit, and output two square wave signals with different pulse widths to the TDC module; the phase difference signal is converted into a corresponding digital signal by the TDC module, and output The sign bit indicating the positive and negative of the phase difference; the digital filter uses a proportional-in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More