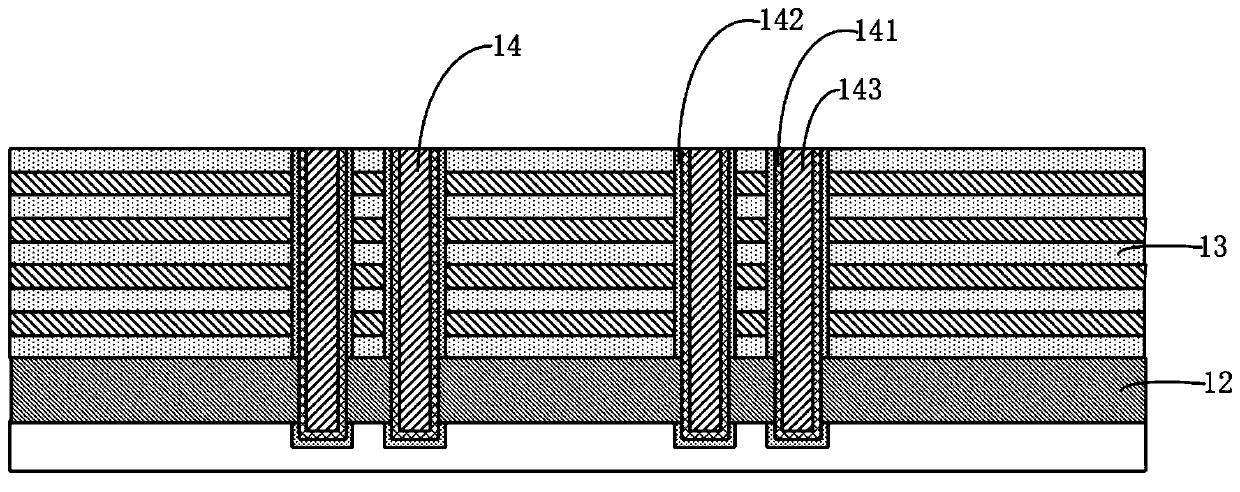

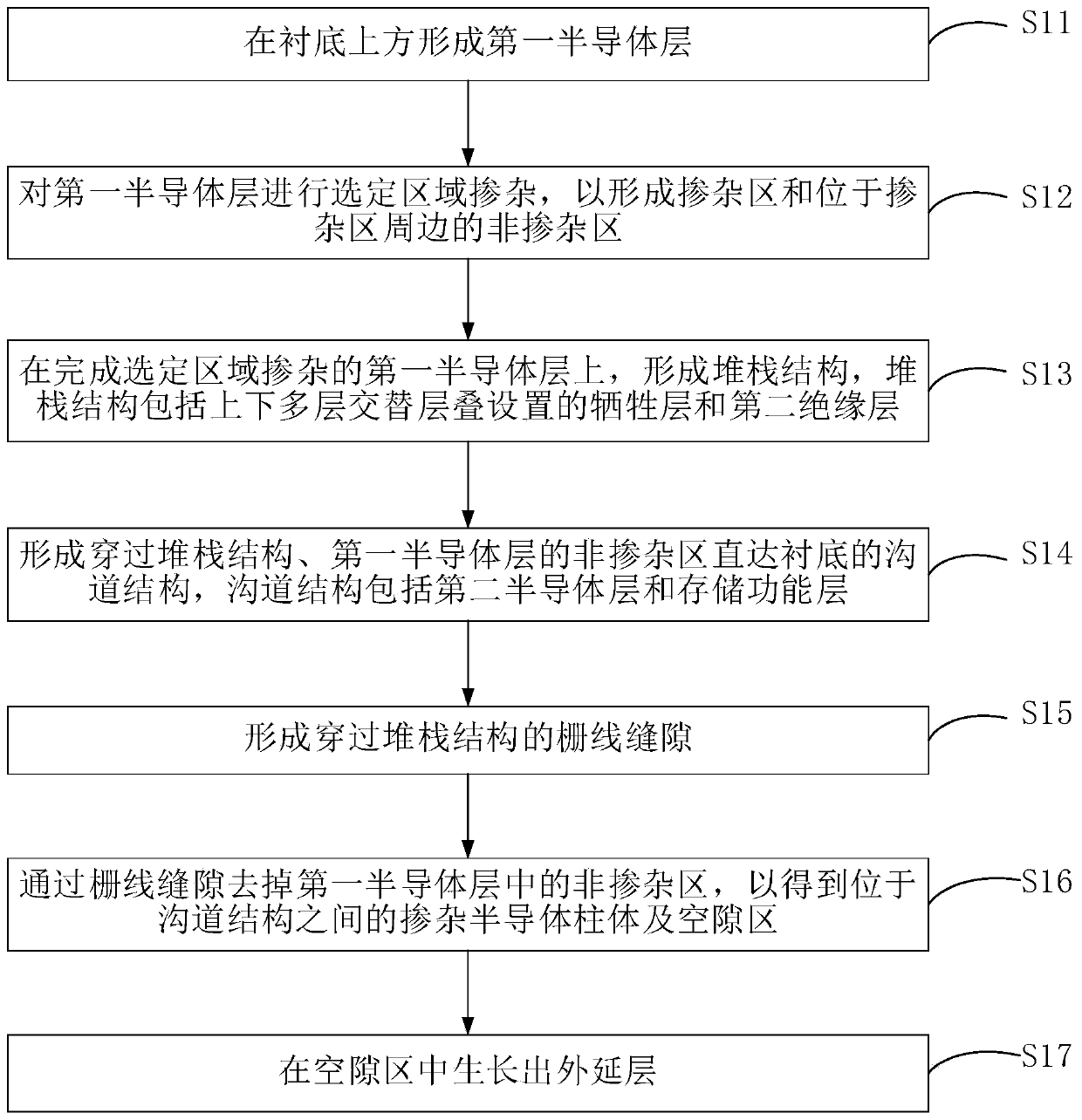

NAND memory and manufacturing method thereof

A manufacturing method and memory technology, applied in the field of memory, can solve problems such as film layer collapse, unstable channel structure, and affecting the support effect of the stack structure, and achieve the effect of ensuring stability and avoiding partial collapse of the film layer or the entire peeling off

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. In particular, the following examples are only used to illustrate the present invention, but not to limit the scope of the present invention. Likewise, the following embodiments are only some of the embodiments of the present invention but not all of them. All other embodiments obtained by those skilled in the art without creative efforts all fall within the protection scope of the present invention.

[0026] In addition, the directional terms mentioned in the present invention, such as [top], [bottom], [front], [back], [left], [right], [inside], [outside], [side], etc., only is the direction with reference to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention. In the figures, structurally similar elements are denoted by the same refer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More