Three-dimensional memory and preparation method thereof

A memory, three-dimensional technology, applied in the semiconductor field, can solve the problems affecting the electrical performance of the three-dimensional memory, the reduction of the yield of the three-dimensional memory, and the height of the gate gap stack, so as to reduce the risk of tilt, improve the contour distortion, and improve the electrical performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

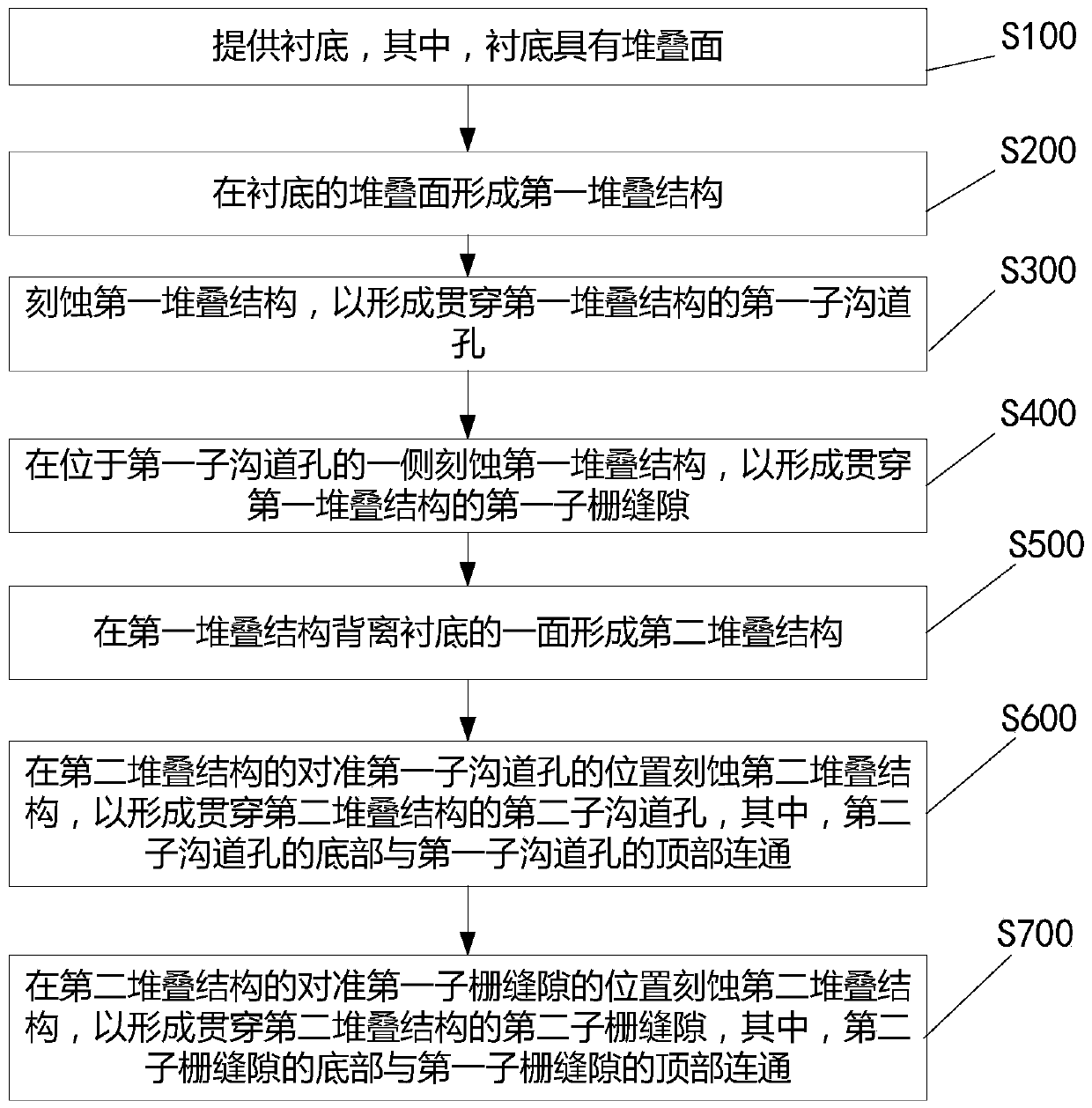

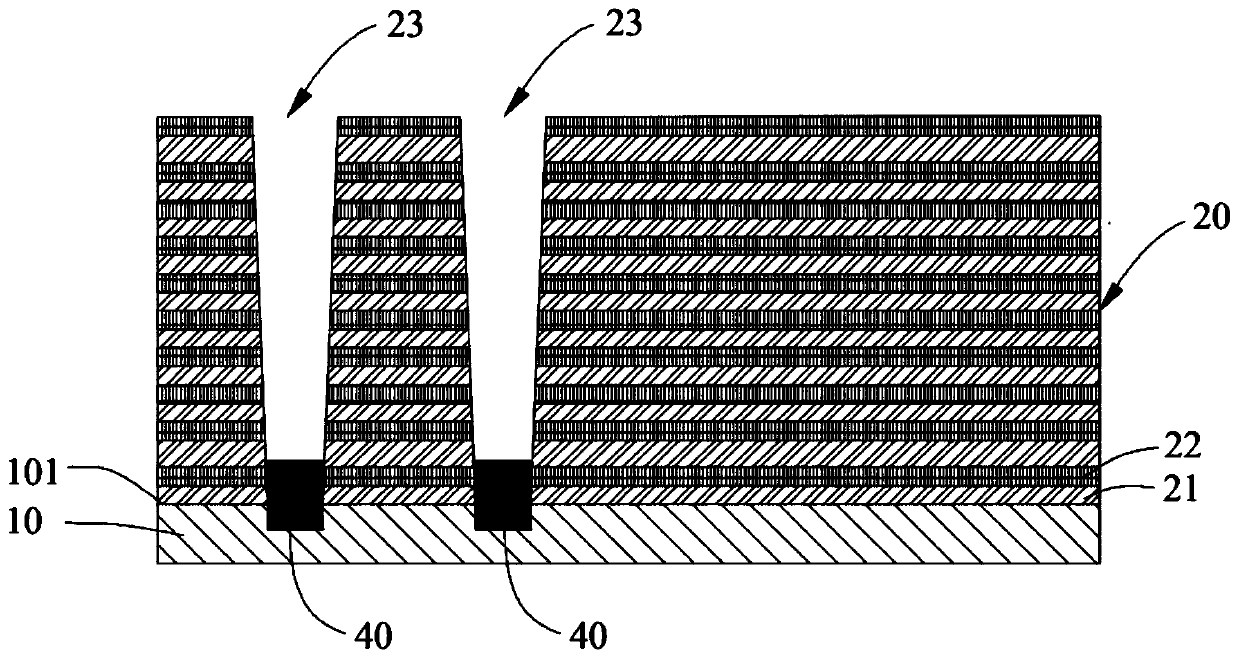

[0049] Specific embodiments of the present invention will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the invention are shown in the drawings, it should be understood that the invention may be practiced in other ways than those described herein, and therefore, the invention is not limited by the following embodiments.

[0050] A three-dimensional (3D) memory is mainly used as a non-volatile flash memory. The two main non-volatile flash memory technologies use NAND (NAND) and NOR (NOR) structures. Compared with NOR memory, the writing speed in NAND memory is fast, the erasing operation is simple, and smaller memory cells can be realized, thereby achieving higher storage density. Therefore, the 3D memory using the NAND structure has been widely used.

[0051] With the increase of the number of layers and the stack height in the three-dimensional NAND memory, in order to increase the storage density, a high as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More