LDPC coding and decoding method and system

A technology of encoding, decoding and encoding, which is applied in the field of LDPC encoding and decoding methods and systems, can solve problems such as communication interruption or occupying too many logic resources, and achieve the effects of improving adaptability and flexibility, saving logic resources, and avoiding communication interruption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

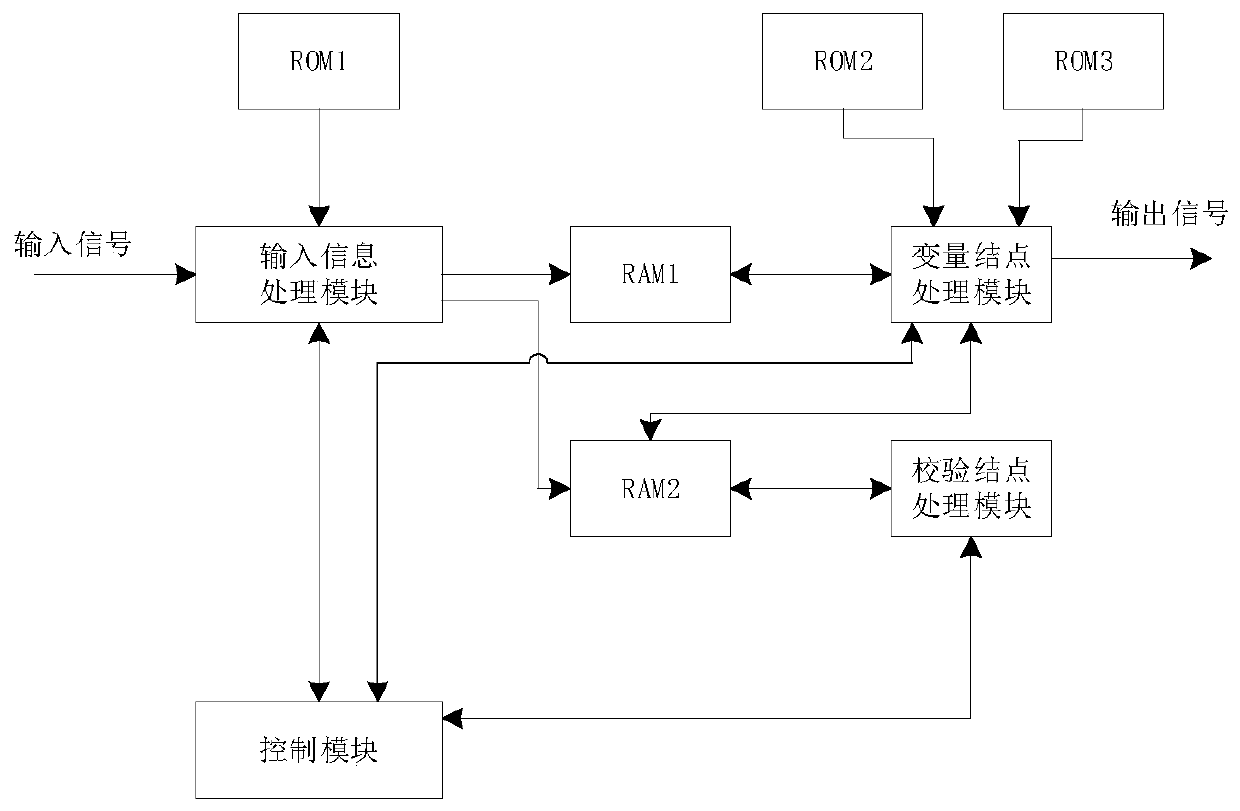

[0044] Embodiment 1 of the present invention provides an LDPC encoding and decoding method. To a certain extent, it is used to solve the problem of communication interruption or occupying more logic resources during the current LDPC codec reconfiguration process. The partial reconfigurable function of FPGA is used to realize the LDPC codec function of different code lengths, while avoiding reconfiguration. Conserve FPGA logic resources while communication interruption occurs. LDPC code is a block error-correcting code with a sparse parity check matrix, which is suitable for almost all channels. Its performance is close to the Shannon limit, and its description and implementation are simple, easy to carry out theoretical analysis and research, and the decoding process is simple and feasible. Parallel operation, suitable for hardware implementation.

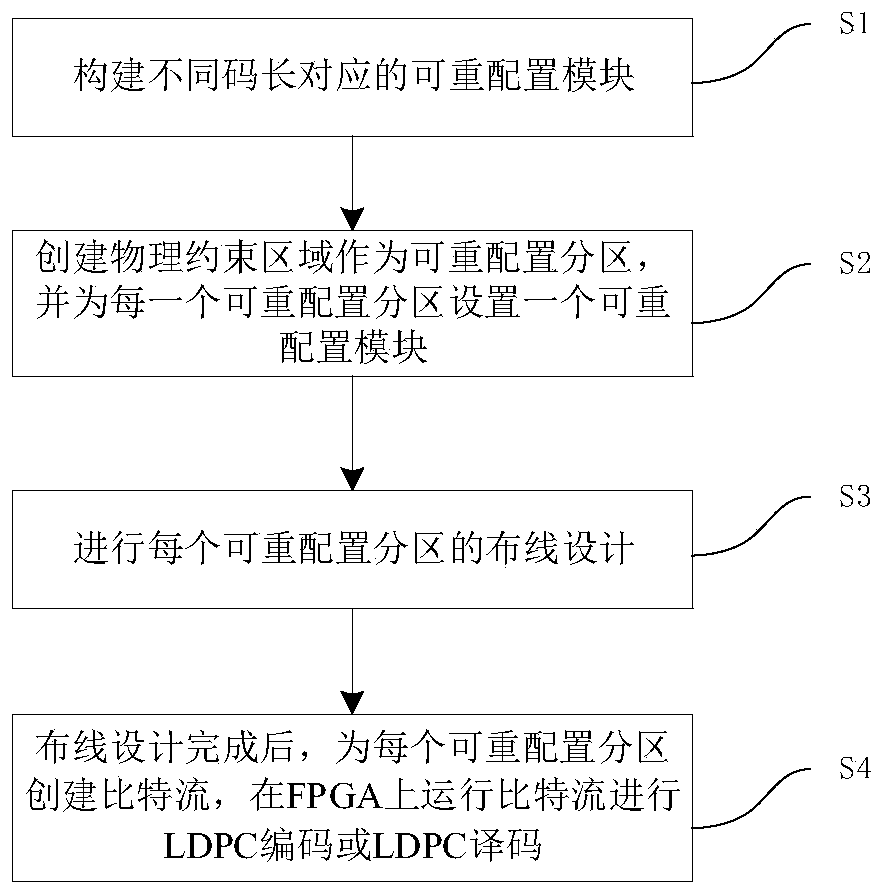

[0045] figure 1 A schematic flow chart of an LDPC encoding and decoding method provided by an embodiment of the present inventi...

Embodiment 2

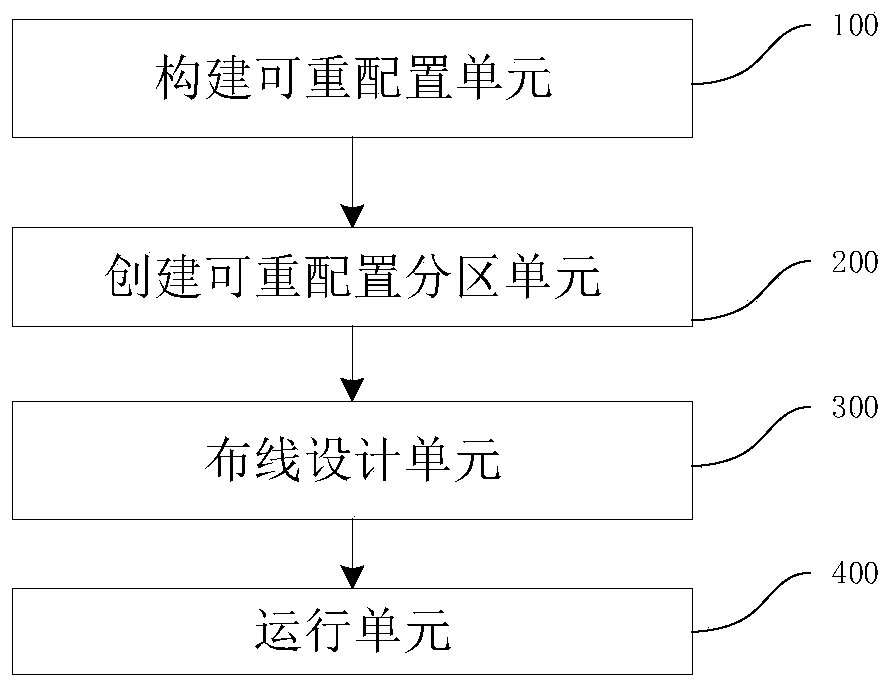

[0090] This embodiment provides an LDPC encoding and decoding system for executing the method described in Embodiment 1, such as image 3 As shown, it is a structural block diagram of a kind of LDPC encoding and decoding system of the present embodiment, including:

[0091] Building a reconfigurable unit 100: used to build reconfigurable modules corresponding to different code lengths, the reconfigurable modules include: LDPC encoding reconfigurable modules or LDPC decoding reconfigurable modules;

[0092] Creating a reconfigurable partition unit 200: used to create a physically constrained area as a reconfigurable partition, and set a reconfigurable module for each reconfigurable partition;

[0093] Wiring design unit 300: for performing wiring design of each reconfigurable partition;

[0094] Execution unit 400: used to create a bit stream for each reconfigurable partition after the wiring design is completed, and run the bit stream on the FPGA to perform LDPC encoding or L...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com