Cascading method of full-interconnection AXI bus

A fully interconnected and cascaded technology, applied in instruments, electrical digital data processing, etc., can solve the problem of inability to realize simultaneous communication of multiple MASTER master devices, reduce system bus scalability and reusability, and limit system bus bandwidth and transmission. Efficiency and other issues, to achieve the effect of supporting parallel communication capabilities, reducing the difficulty of timing closure, and ensuring independence and flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

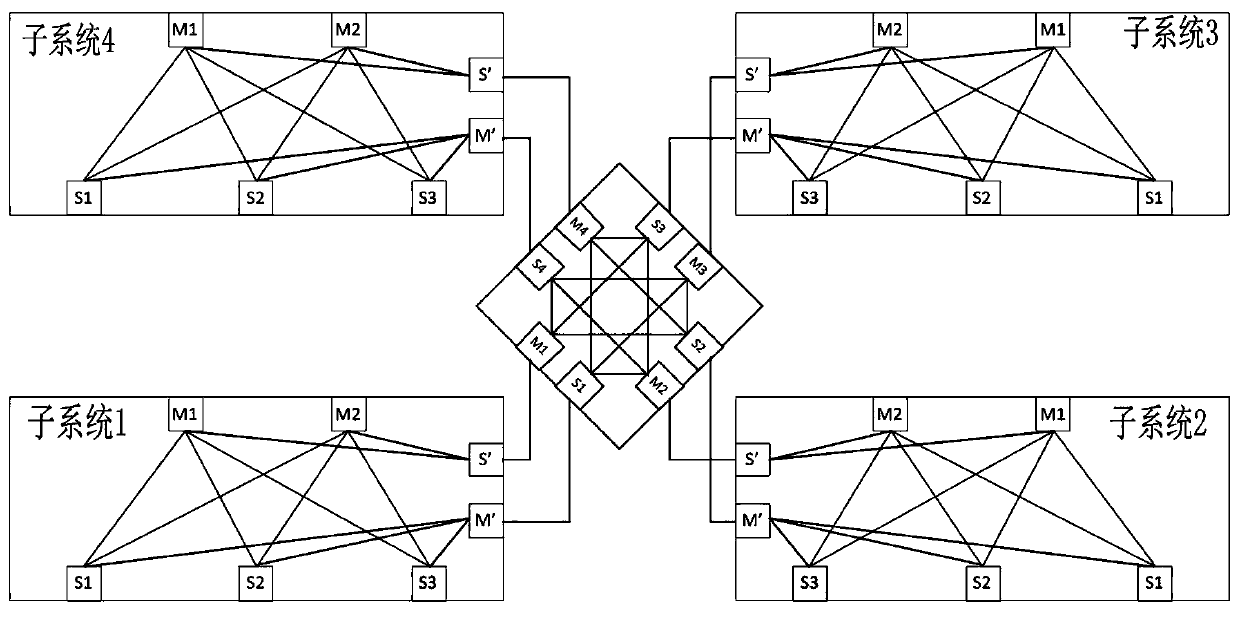

[0016] Attached below figure 1 The present invention will be further described.

[0017] A cascading method of a fully interconnected AXI bus, comprising the steps of:

[0018] a) N subsystems are set in the AXI bus, and N is a positive integer greater than or equal to 2. The subsystem includes several master terminals and several slave terminals, and each master terminal is connected to each slave terminal;

[0019] b) Set the cascade central unit, N groups of interaction devices I are set in the cascade central unit, each subsystem is provided with an interaction device II, and each subsystem communicates with the corresponding interaction device of the cascade central unit through the interaction device II Ⅰ interconnected with each other;

[0020] c) when a master in a subsystem accesses a slave in the subsystem, the master directly accesses the slave;

[0021] d) When a master terminal in a subsystem accesses a slave terminal in another subsystem, the master terminal i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More