Parallel test system for multi-channel intermittent disconnection faults based on fpga

A technology for disconnecting faults and testing systems. It is applied in the direction of electronic circuit testing, measuring electricity, and measuring devices. It can solve problems such as lack of testing methods, high testing missed detection rate, and low efficiency, so as to avoid missed testing and save testing resources. , Improve the effect of testing difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to more clearly understand the above objects, features and advantages of the present application, the present application will be further described in detail below with reference to the accompanying drawings and specific embodiments. It should be noted that the embodiments of the present application and the features of the embodiments may be combined with each other in the case of no conflict.

[0034] In the following description, many specific details are set forth to facilitate a full understanding of the present application. However, the present application can also be implemented in other ways different from those described herein. Therefore, the protection scope of the present application is not subject to the following disclosure. Restrictions to specific embodiments.

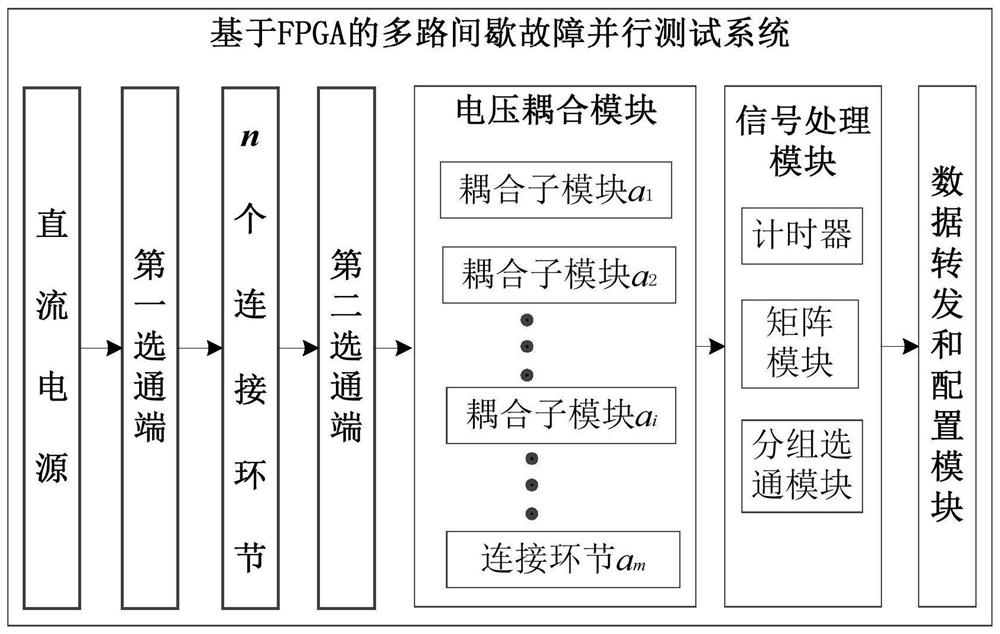

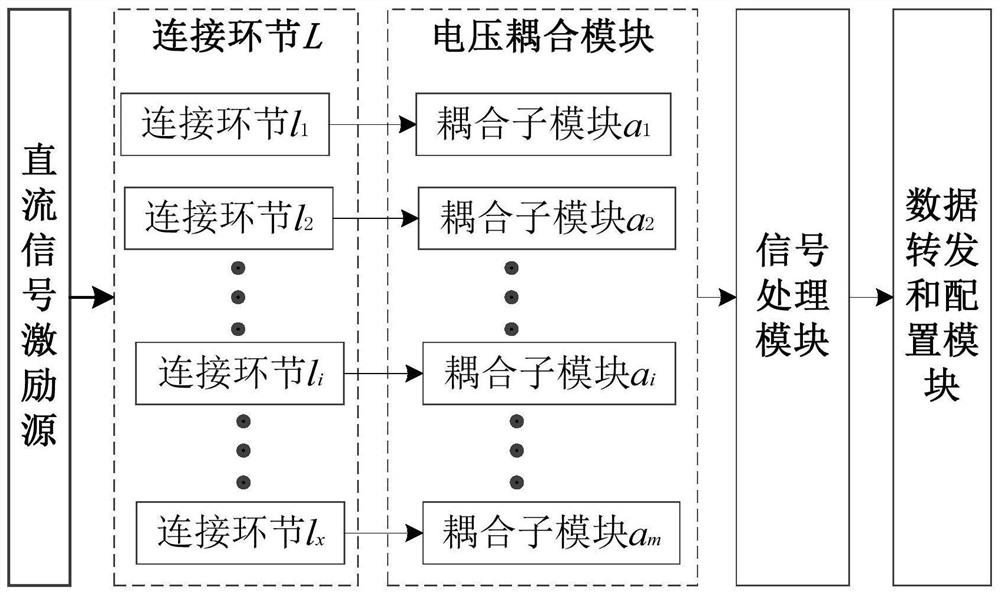

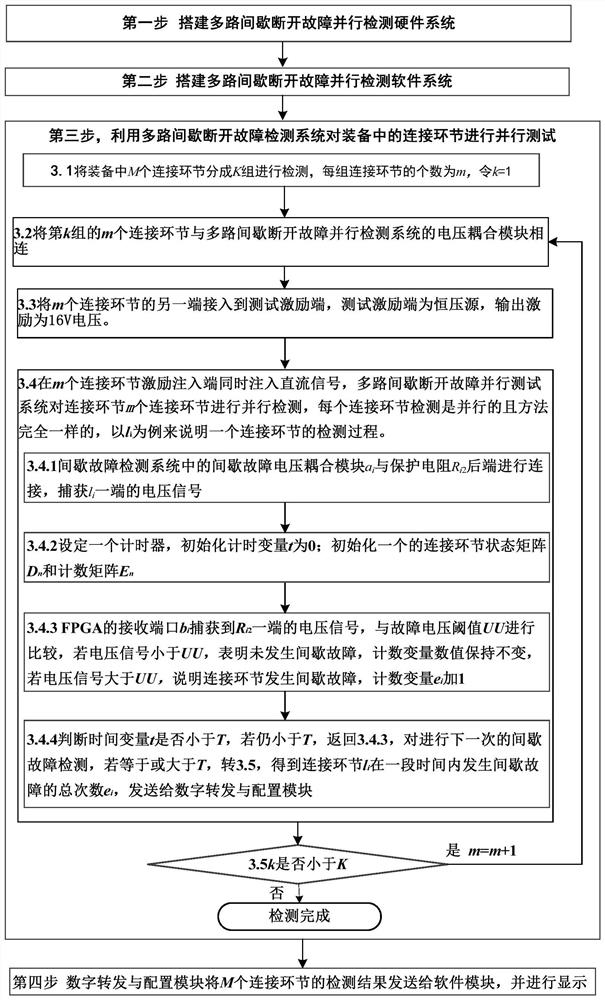

[0035] like figure 1As shown, this embodiment provides an FPGA-based multi-channel intermittent disconnection fault parallel test system, which is suitable for the intermittent disconnec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More