Memory and forming method thereof, and memory cell array and driving method thereof

A storage unit, memory technology, applied in static memory, digital memory information, information storage, etc., can solve problems such as poor performance of split-gate flash memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] As mentioned in the background, the performance of flash memory is poor.

[0046] The reasons for the problems are described below in conjunction with the accompanying drawings.

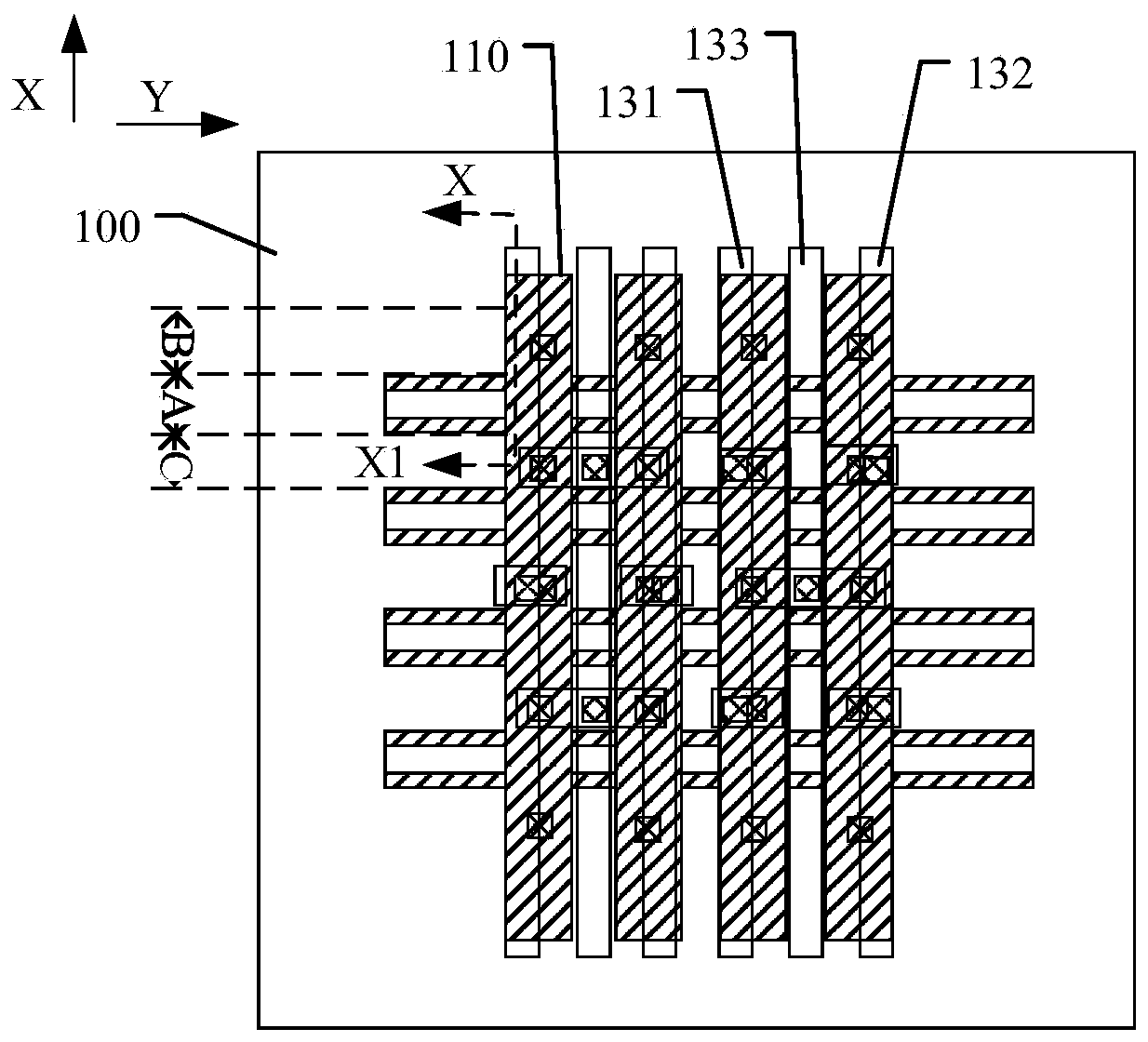

[0047] figure 1 is a schematic diagram of a memory cell array.

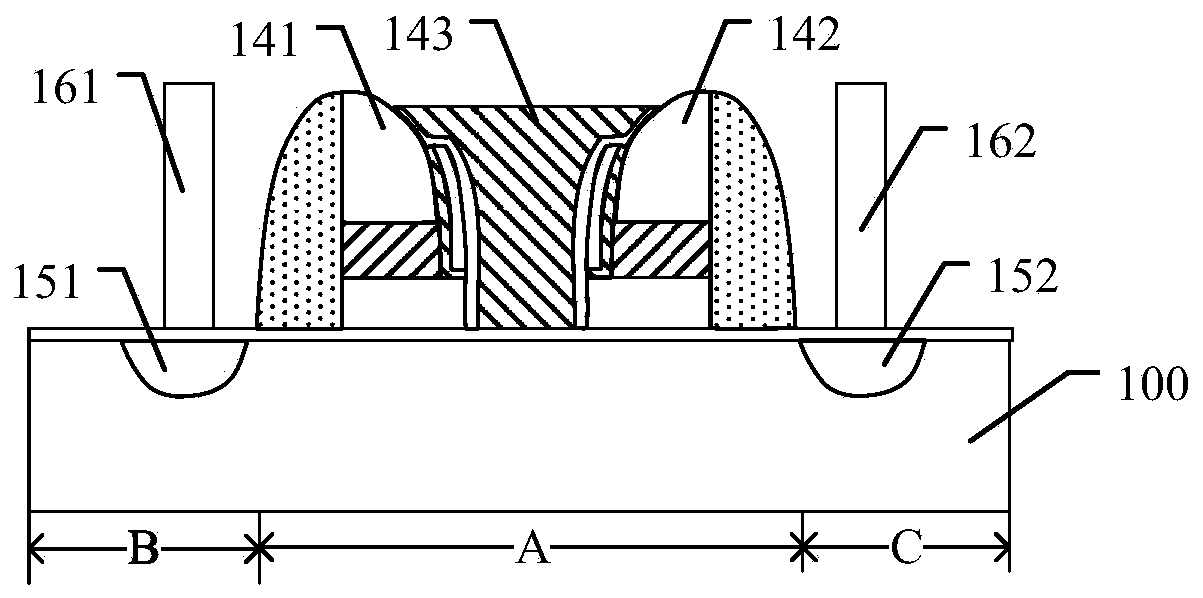

[0048] An array of memory cells, see figure 1 , comprising: a semiconductor substrate 100, the semiconductor substrate 100 comprising: several parallel and discrete active regions 110 arranged in parallel along the second direction Y, and an isolation structure surrounding the active regions 110 (not shown in the figure) , the active regions 110 extend along the first direction X, and each of the active regions 110 in the first direction X includes several memory cell regions, and each memory cell region includes: a storage region A and a storage region located in the storage region Source region B and drain region C on both sides of A; several source regions, and one source region in the source region B; several drain regions...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More