FPGA configuration file compression and decompression method based on partition reference technology

A configuration file and decompression technology, applied in the electronic field, can solve the problem of time-consuming configuration process, and achieve the effect of saving engineering expenses, reducing file content, and improving compression rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

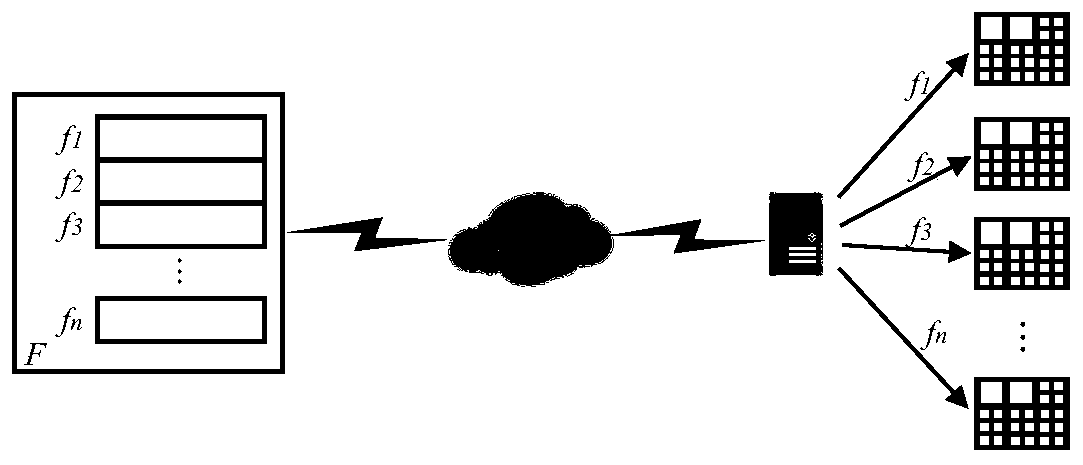

[0042] A kind of FPGA configuration file compression and decompression method based on partition reference technology of the present invention comprises the following steps:

[0043] S1, FPGA configuration file partition;

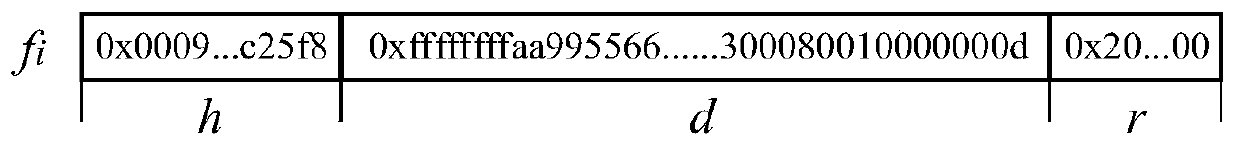

[0044] The FPGA configuration file can be divided into three parts according to the content: header information, configuration data information and tail redundant information.

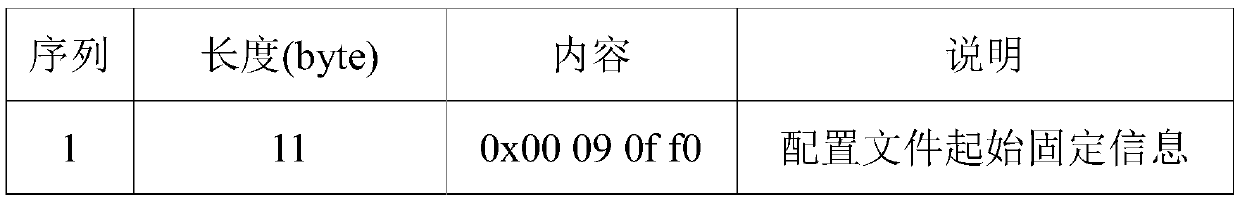

[0045] see figure 2 , the present invention defines the FPGA configuration file f i =(h,d,r),i=1,2,3,...,n, the first part of the header information h, including project name, compilation time, target chip model and other information that has nothing to do with the configuration content; the second part is The configuration data information d includes the binary codes of various resources in the target chip; the third part is the tail redundant information r, which includes several empty instruction operations.

[0046] According to the content classification of the above-mentio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More