High-speed interconnection network topology discovery method and device, medium and high-performance computing system

A high-performance computing, high-speed interconnection technology, applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve problems such as shortening interconnection network debugging time, inspection, and inability to perform interconnection network topology.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

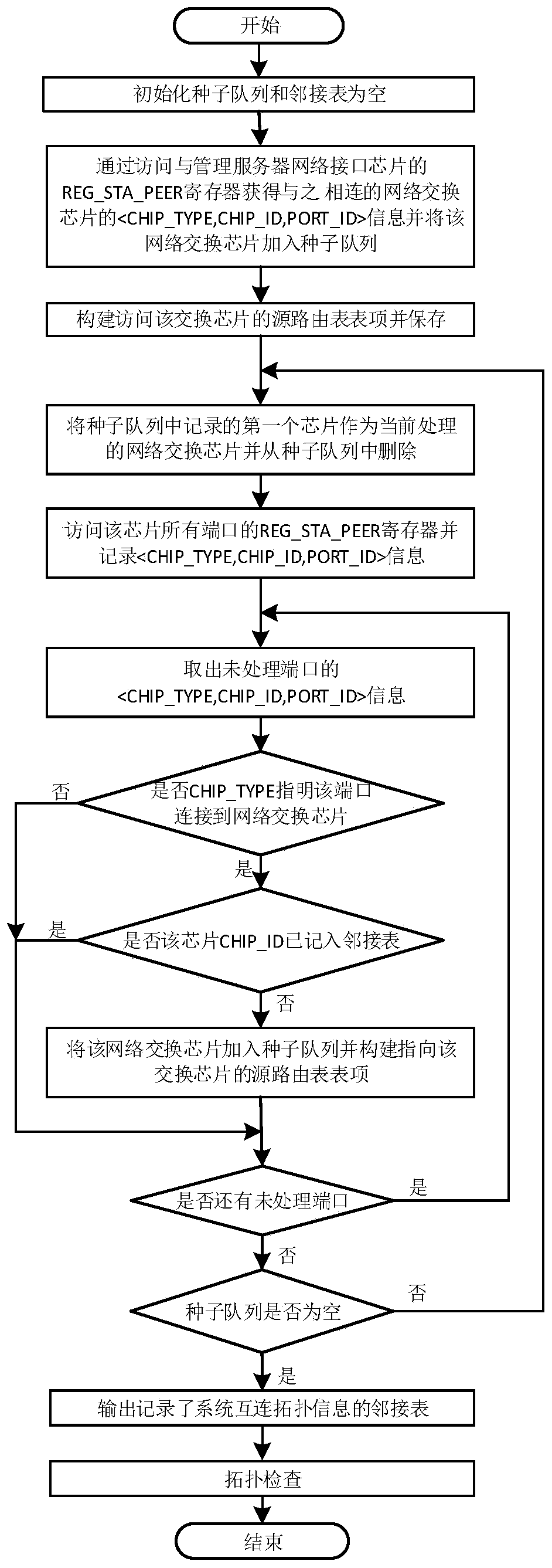

[0047] Such as figure 1 The implementation steps of the high-speed interconnection network topology discovery method used in the high-performance computing system in this embodiment include:

[0048] 1) Initialize the seed queue and adjacency list to be empty;

[0049] 2) access the peer tag information in the network interface chip of this node, and add the network interface chip recorded in the peer tag information to the seed queue;

[0050] 3) Constructing a source routing table entry pointing to the peer network interface chip, the source routing table is a data structure allocated in the memory of the management server to record the round-trip routing path between the management server and each network chip;

[0051] 4) taking the first network switching chip in the seed queue as the current network switching chip and deleting it from the seed queue;

[0052] 5) Access the peer tag information of all ports of the current network switching chip;

[0053] 6) Take out th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More