Extraction method of source-drain resistance of field effect transistor

A field-effect transistor, source-drain resistance technology, applied in the measurement of resistance/reactance/impedance, measurement of electricity, measurement of electrical variables, etc., can solve the problems of increased test time, source-drain resistance error, occupied chip area, etc., to eliminate extraction The effect of error, improving extraction accuracy, and improving test speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

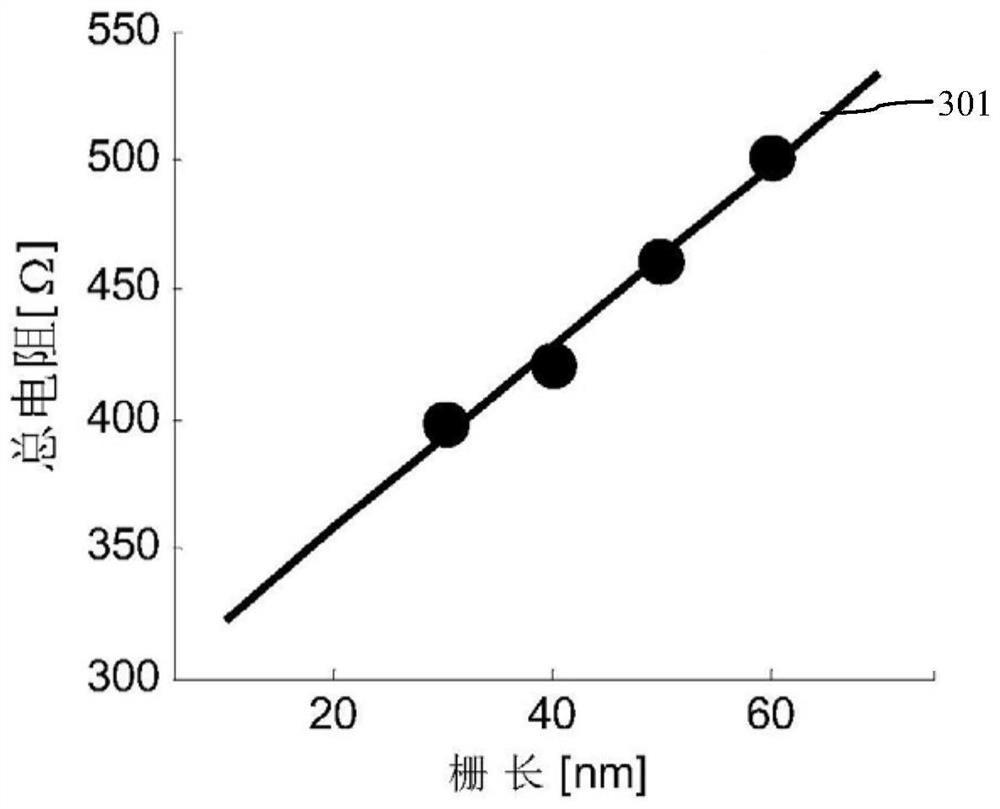

[0069] like Figure 4 shown is a flowchart of a method for extracting source-drain resistance of a field effect transistor according to an embodiment of the present invention; Figure 5 shown are the first electrical characteristic curve and the third electrical characteristic curve obtained in the embodiment of the present invention; as Image 6 As shown, is the second relationship curve 502 obtained in the embodiment of the present invention; the method for extracting the source-drain resistance of the field effect transistor in the embodiment of the present invention includes the following steps:

[0070] Step 1: Test to obtain a first electrical characteristic curve 401 formed by the absolute value of the drain current and the gate voltage of the linear region of the field effect transistor.

[0071] Figure 5 , the drain current is I D Indicates that the gate voltage is represented by V G means that the ordinate of the first electrical characteristic curve 401 corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More