Cache consistency protocol verification method and system for on-chip multi-core processor, and medium

A multi-core processor and verification method technology, which is applied in the field of Cache (cache) consistency protocol verification of on-chip multi-core processors, can solve the problems of inability to fully test the correctness of the protocol, difficult positioning, and low efficiency, and achieves easy detection of design errors. , the effect of accurately locating the wrong scene

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the content of the present invention more clear and understandable, the content of the present invention will be described in detail below in conjunction with specific embodiments of the present invention and accompanying drawings.

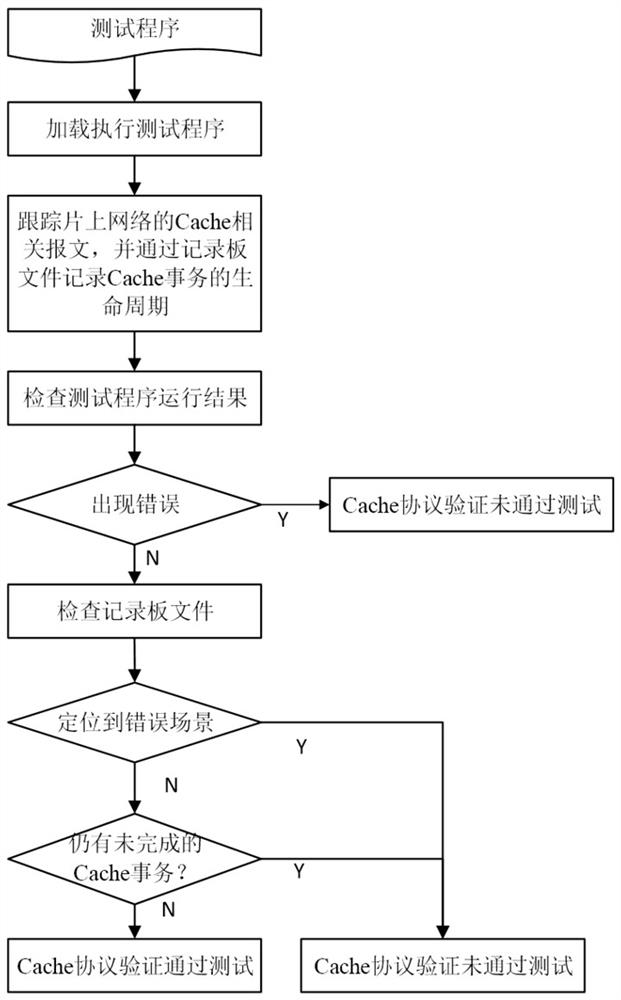

[0033] like figure 1 As shown, the steps of the on-chip multi-core processor Cache consistency protocol verification method in this embodiment include:

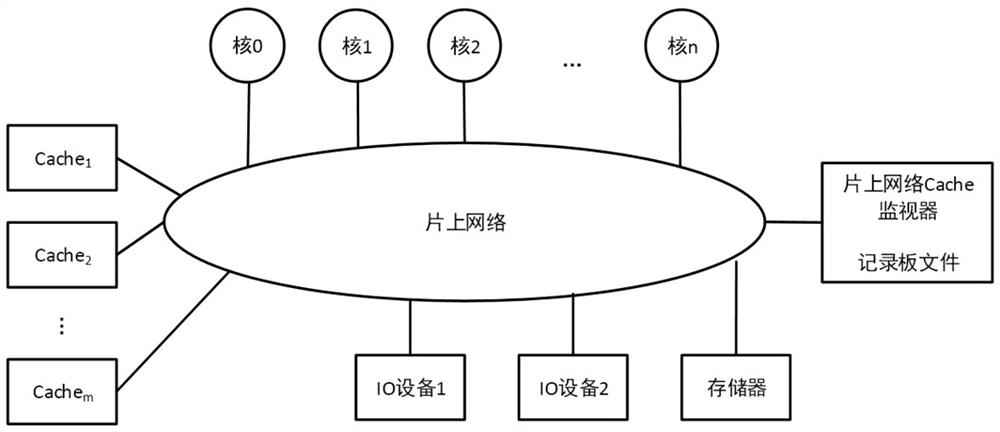

[0034] 1) Load and execute the test program for the on-chip multi-core processor that executes the Cache protocol to be verified, and track the Cache-related messages of the on-chip network, and record the life cycle of the Cache transaction through the record board file;

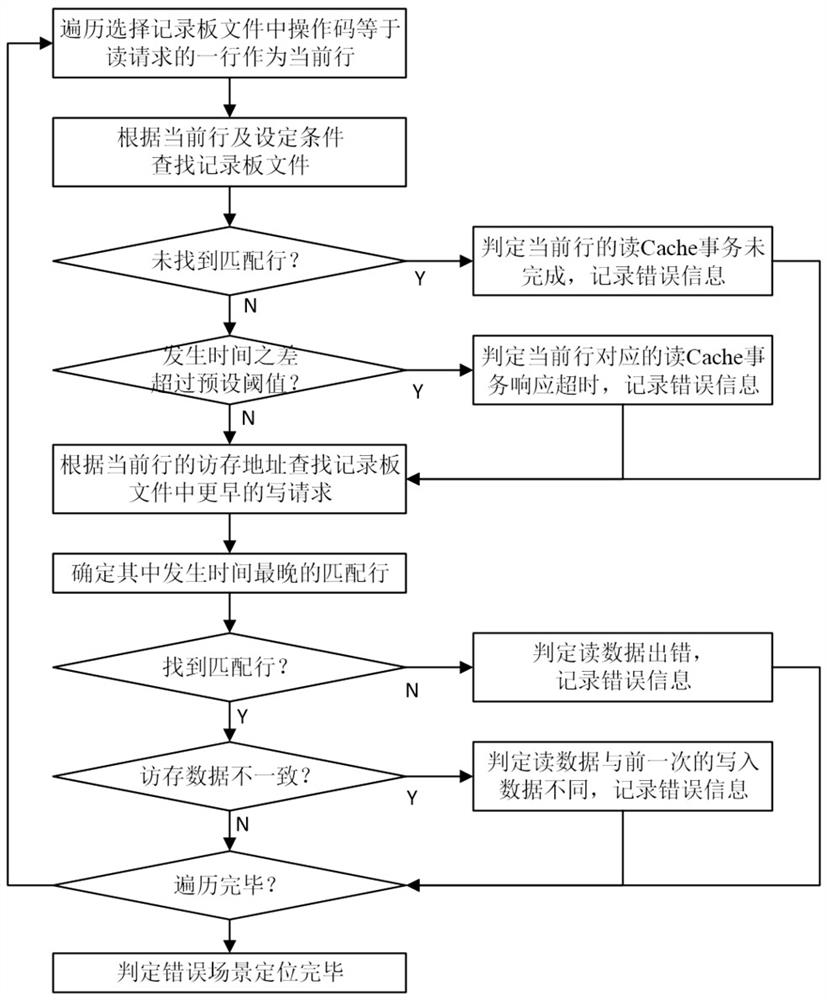

[0035]2) Check whether there is an error in the running result of the test program. The error means that the memory access data read by the read request for the same memory access address is inconsistent with the memory access data written by the last write request of the memory access address, or the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More