Array substrate and manufacturing method thereof

A technology of array substrates and bases, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problem of a large number of manufacturing processes, and achieve the effect of reducing the number of photomasks and manufacturing processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

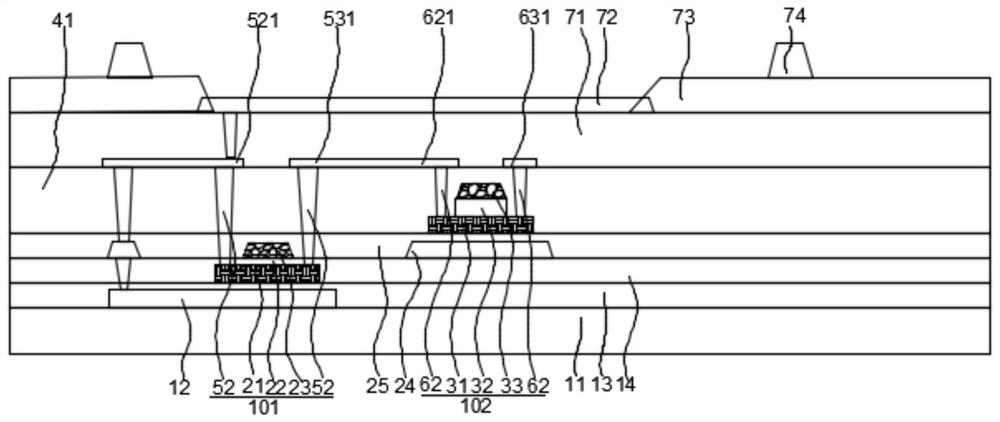

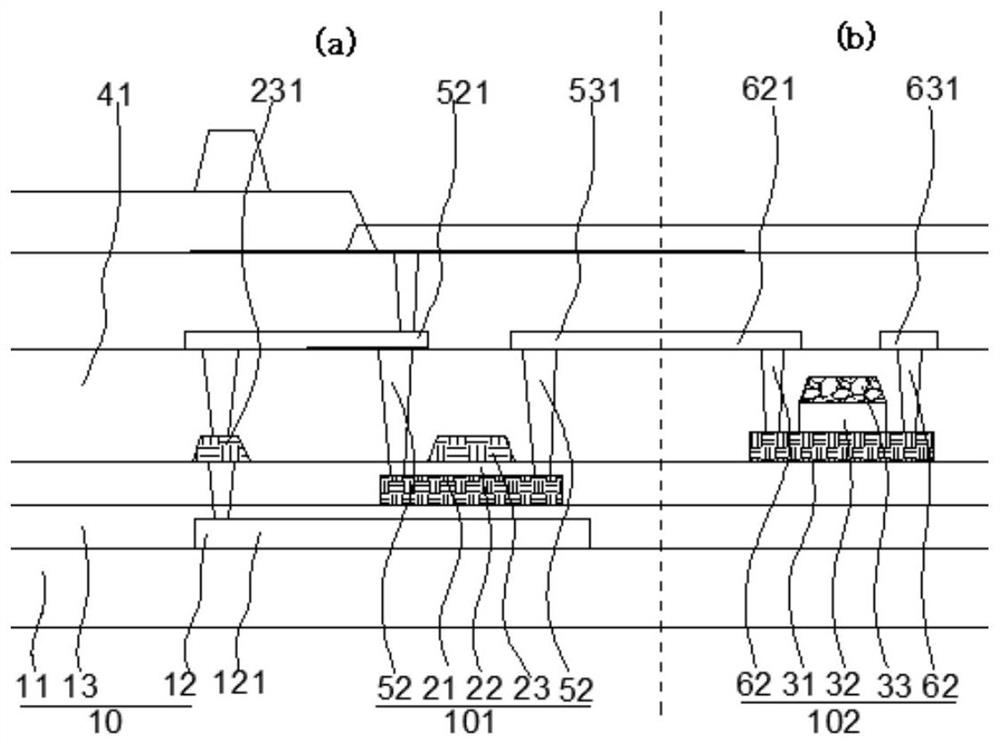

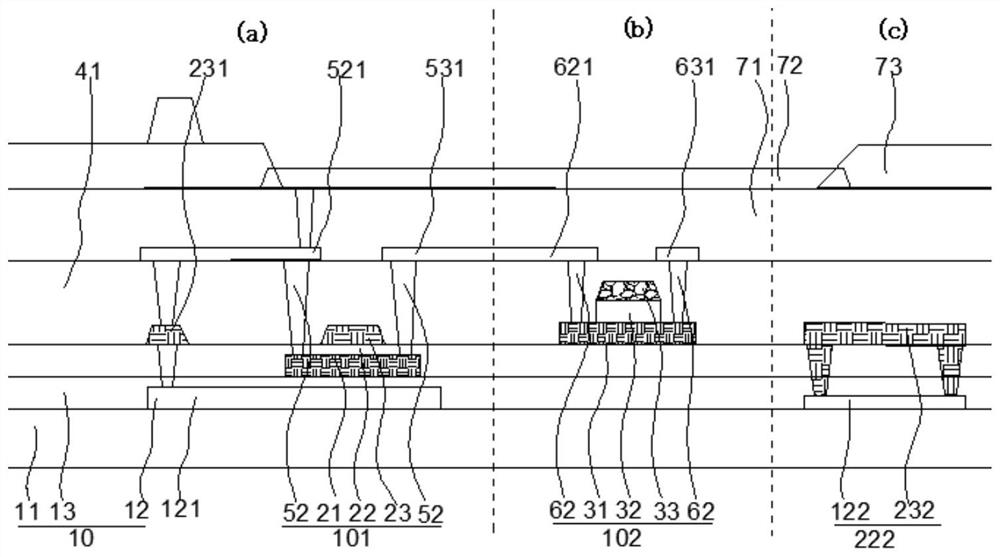

[0041] see figure 2 As shown, an array substrate includes: a substrate 10; a first TFT 101 located in the region (a) is disposed on the substrate, and the first TFT 101 includes a first active layer 21 disposed on the substrate, disposed on The first gate insulating layer 22 on the substrate 10 and the first active layer 21 and covering the first active layer 21 , and the first gate disposed on the first gate insulating layer 22 electrode 23; the second TFT102 located in the (b) region is disposed on the first gate insulating layer 22, and the second TFT102 includes a second active active layer disposed on the first gate insulating layer 22 layer 31 , a second gate insulating layer 32 disposed on the second active layer 31 , and a second gate 33 disposed on the second gate insulating layer 32 .

[0042] Wherein the material of the first gate 23 is the same as that of the second active layer 31 , and is an integrally formed structure. The material of the second active layer ...

Embodiment 2

[0046] see image 3 , this embodiment is the same or similar to Embodiment 1, the difference is:

[0047] The array substrate further includes signal sub-lines 232 located in the region (c). The material of the signal sub-line 232 is the same as that of the first gate 23 and the second active layer 31 , and is an integrally formed structure. Specifically, the signal sub-line 232 can be formed at the same time as the second active layer 31 and the first gate 23 are formed, and the formation method includes but is not limited to: first forming the entire surface of the oxide semiconductor film layer , and then simultaneously form the patterned first gate 23 , the second active layer 31 , and the signal sub-lines 232 through processes such as exposure and etching. In some embodiments, in order to reduce the resistance value of the first gate 23 and the signal sub-line 232 made of oxide semiconductor, it can be processed by Plasma, such as N2, He, N2O, H2, etc. or their mixed ga...

Embodiment 3

[0053] see Figure 5 , this embodiment is the same or similar to Embodiment 1 to Embodiment 2, the difference is that:

[0054] The multifunctional metal layer 12 also includes a capacitive sublayer 123 on the substrate 11, and the first gate insulating layer 22 is provided with a first capacitive electrode 331 corresponding to the capacitive sublayer 123, The first gate insulating layer 22, the first gate 23, the second TFT 102, and the first capacitance electrode 331 are provided with a cover covering the first gate insulating layer 22, the first gate 23. The second TFT 102 , the first and the interlayer insulating layer 41 of the capacitor electrode 331 , the interlayer insulating layer 41 is provided with a second capacitor electrode 531 corresponding to the first capacitor electrode 331 .

[0055] The first capacitor electrode 331 is made of the same material as the second gate 531 , and is integrally formed. Specifically, the formation method includes but is not limite...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More