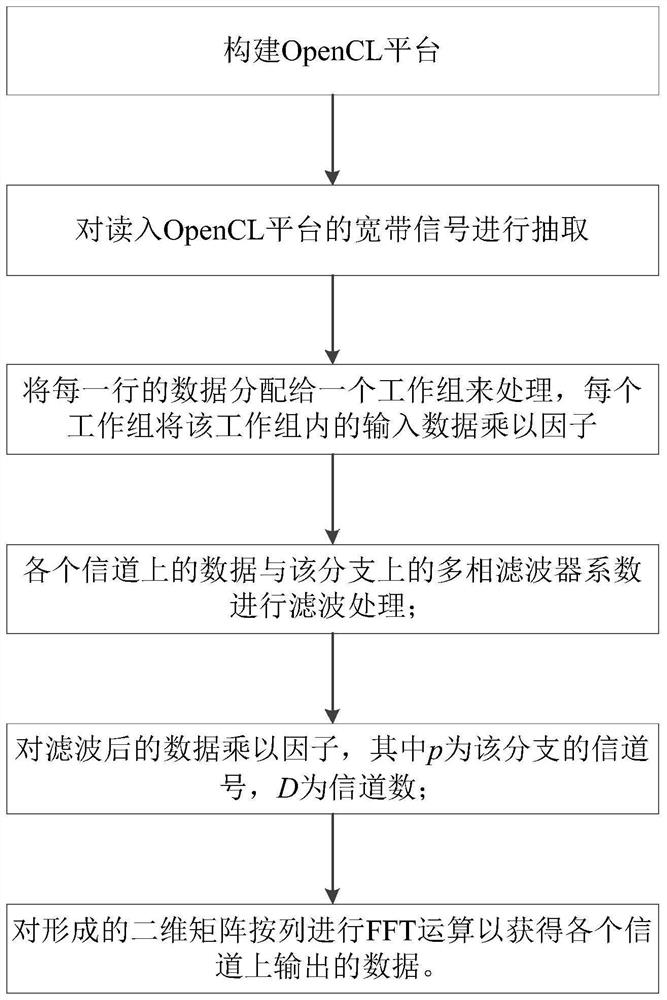

A broadband parallel channelized receiving method based on embedded gpu

A receiving method and channelized technology, applied in the field of broadband parallel channelized receiving based on embedded GPU, can solve the problems of inconvenience, high development cost, poor portability, etc., and achieve good portability, low power consumption, and improved processing. The effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

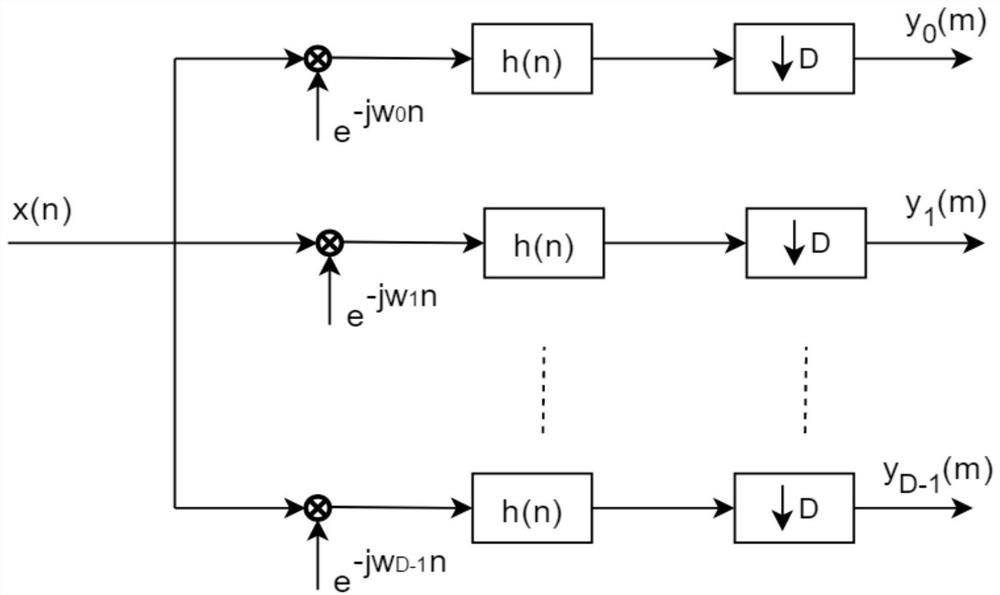

[0050] The traditional digital channelization structure is based on the low-pass filter bank digital channelization structure, such as figure 2 , this structure divides the broadband signal x(n) into K signals, and each signal is first moved to the baseband through down-conversion processing, then low-pass filtering is performed through a low-pass filter, and finally the data is changed through the decimator. rate to finally obtain the signal. The digital channelization structure based on low-pass filter bank is expressed as:

[0051]

[0052] Among them, h LP (n) represents a low-pass filter.

[0053] Expand the above formula to get:

[0054]

[0055] like:

[0056] x p (m-i)=x(mD-iD-p),

[0057] h p (i)=h LP (iD+p)

[0058] can get:

[0059]

[0060] take further

[0061]

[0062] but

[0063]

[0064]

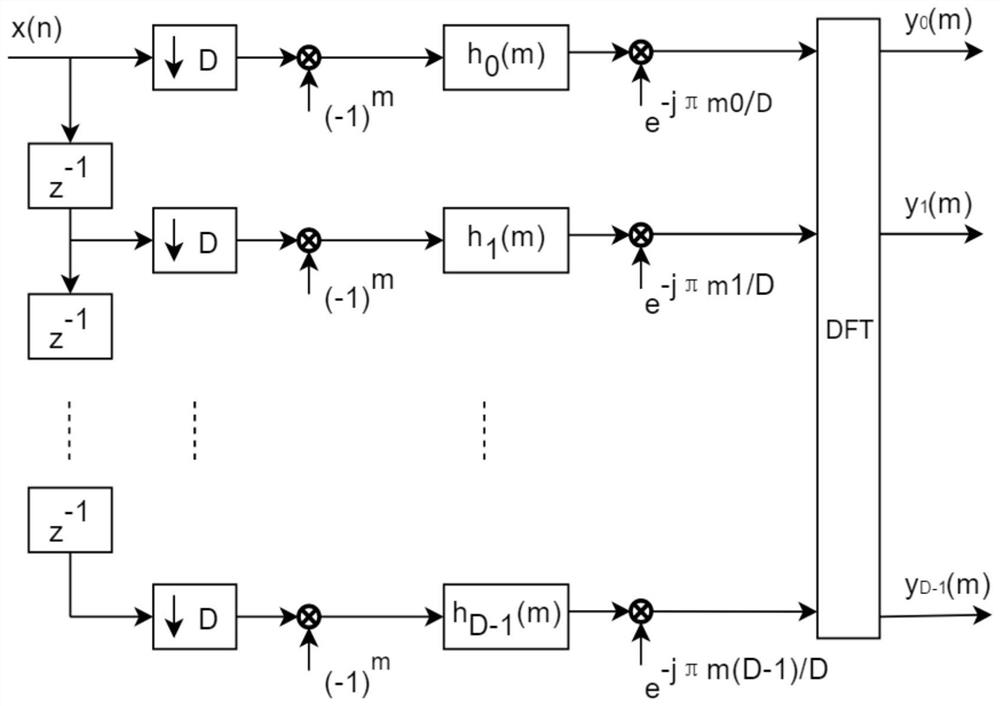

[0065] Substituting the above two equations into the digital channelization structure based on low-pass filter banks can obtain the mathematic...

Embodiment 2

[0073] Such as Figure 4 , in the OpenCL platform model, an OpenCL device contains multiple computing units, and each computing unit contains multiple processing elements. These processing elements are also called work items. OpenCL computing tasks are composed of these mutually independent processing elements. implement. According to different access permissions of threads, each processing element can access four storage spaces with different permissions: private memory, local storage area, constant memory and global memory. The way they are used in the program largely determines the performance of the program. , generally speaking, their size and access speed are different.

[0074] The index of the wideband digital channelized receiver designed in this embodiment is to divide the wideband signal with a bandwidth of 6.144MHz into 3KHz, and divide it into 2048 channels in total. Due to the large number of channels, if only a single-stage channelization process is used, a la...

Embodiment 3

[0084] In the polyphase DFT channelization structure, it is necessary to take the signal points on each channel and perform DFT to obtain the corresponding channelization processing results on the channel. In this paper, the fast Fourier transform (FFT) is used [7] to replace DFT processing to improve computational efficiency.

[0085] The input data of DFT is grouped by parity, and the FFT expression can be derived by using the reducibility and periodicity of the rotation factor, which is expressed as:

[0086]

[0087]

[0088] Among them, X 1 (k), X 2 (k) is the sequence obtained after parity grouping of the input sequence x(k) after N / 2 point DFT, is the rotation factor, and N is the signal point to be processed. Through decomposition, the calculation amount of DFT can be effectively reduced. Since N is a positive integer power of 2, The point DFT can continue to be decomposed until it is decomposed into a 2-point DFT. This operation is called a butterfly oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More