Method for detecting and correcting memory data accuracy under IP multiplexing

An accurate and memory technology, applied in the SoC field, can solve the problems of inability to guarantee data consistency, failure to provide write-back function, insufficient configurability, etc., to increase the parity bit, easy to implement, and high reusability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

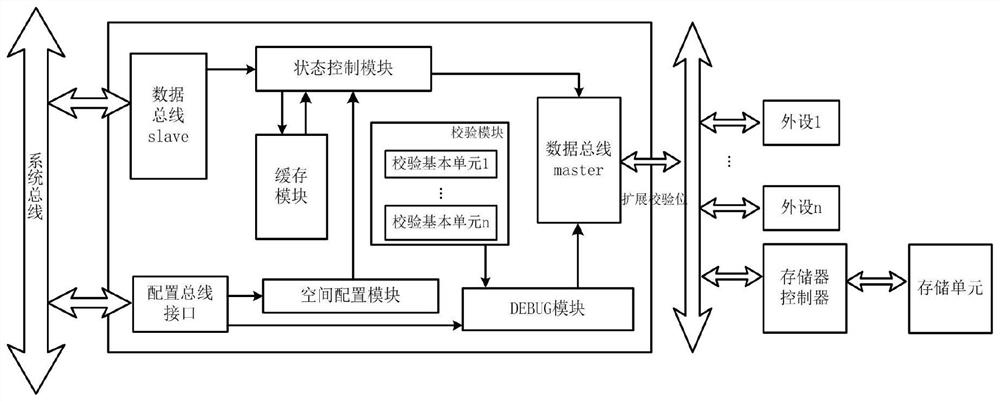

[0033] The invention provides a method for checking the accuracy of memory data under IP multiplexing, such as figure 1 As shown, a transfer bridge with error detection and correction functions is inserted between the system bus and the memory controller to expand the data bit width of the memory controller and increase the check bit; the transfer bridge provides the storage of the check bit Space, share the address line with the data of the system bus.

[0034] Please keep reading figure 1 The transfer bridge includes a data bus slave, a data bus master, a configuration bus interface, a space configuration module, a check module, a DEBUG module, and a buffer module. The system bus is an on-chip bus, and different SoC systems adopt different on-chip bus protocols. The method of the present invention is applicable to different bus protocols, and only needs to be based on the data bus slave, data bus master, and configuration bus interface. The corresponding protocol is designed to...

Embodiment 2

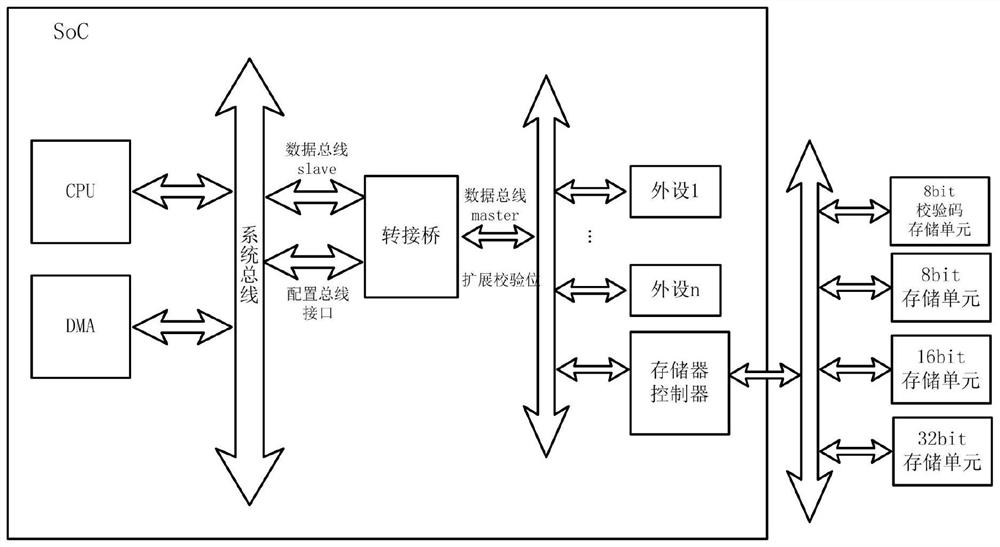

[0046] See image 3 The method of the present invention is used in a SoC circuit, and externally mounted storage units with different data widths, such as 8bit, 16bit, and 32bit storage units for storing data, and an 8bit checksum storage unit for storing check codes. The CPU or DMA accesses the memory controller through the system bus, and the external memory is accessed by the memory controller. The transfer bridge integrated with the ECC check module communicates with the CPU through the data bus slave and connects with the memory controller through the data bus master. Before using the external storage unit, configure the DEBUG module and space configuration module of the transfer bridge through the software program, such as configuring the storage data width of the space occupied by the 8-bit, 16-bit, and 32-bit storage unit, and configure the storage space that enables the ECC check function , Enable write-back function and interrupt alarm function.

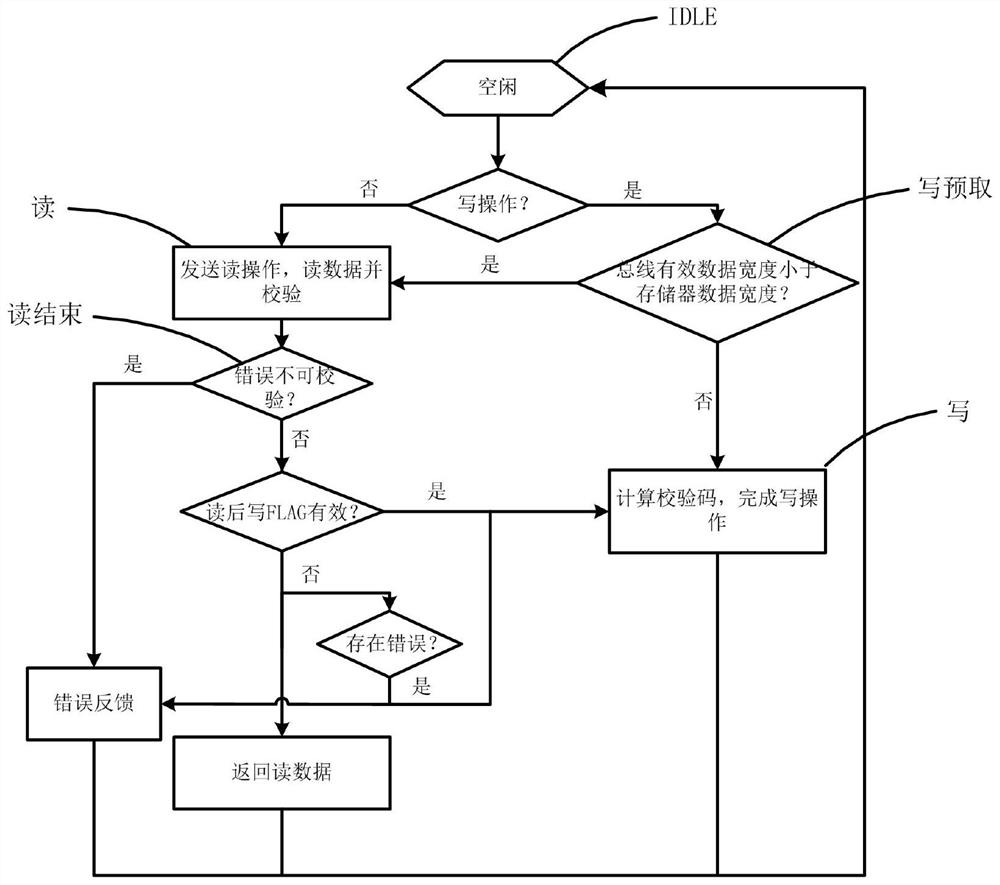

[0047] When the effe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More