Voltage-drop-circuit-based MOS transistor verification fixing architecture and verification method

A MOS tube and circuit technology, applied in the field of MOS tube verification and verification based on voltage drop circuits, can solve the problems of misjudgment, waste of space, and overall design exceeding specifications by designers and verifiers, so as to reduce considerations and costs. , Wide application prospect, reliable effect of design principle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

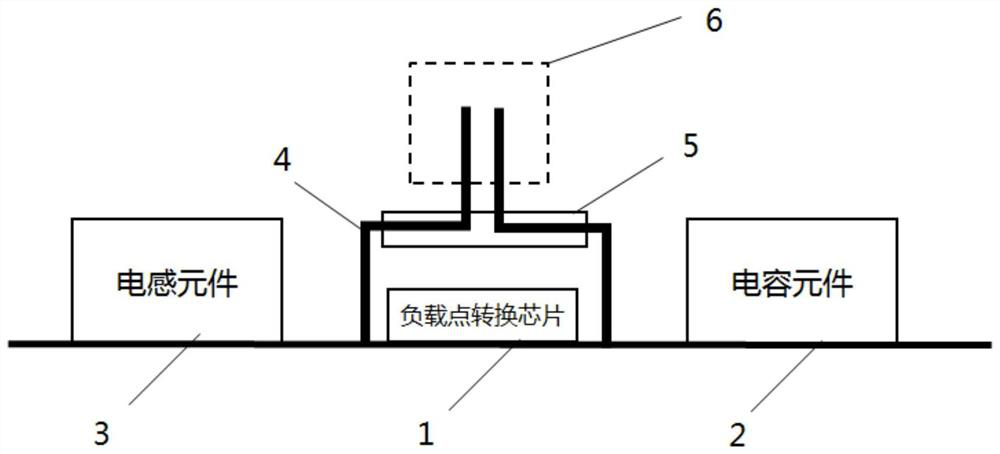

[0026] Such as figure 1 As shown, this embodiment provides a MOS transistor verification and fixed architecture based on a voltage drop circuit, including: the voltage drop circuit includes: a point-of-load conversion chip 1, a capacitive element 2, and an inductive element 3, and the point-of-load conversion chip 1, a frame 4 and an insulating plate 5 are arranged above, and the insulating plate 5 is embedded in the top of the frame 4. The frame 4 includes two low-impedance and high-conduction rods, and the bottom ends of the two low-impedance and high-conduction rods are connected to the capacitive element 2 respectively. , the inductance element 3 is connected, and the tops of the two low-impedance and high-conduction bars constitute the test point 6 for MOS tube verification; the insulating plate is an insulating plastic plate, and the size of the insulating plate is larger than the point-of-load conversion chip; The above architecture is set on the power board by means of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com