Multi-strategy high-precision clock synchronization edge computing server design method

A high-precision clock and edge server technology, applied in the direction of synchronization device, multiplexing communication, time division multiplexing system, etc., can solve the problems of single clock synchronization scheme, easy to be affected by environmental interference, and low precision, and achieve improved The effects of clock synchronization accuracy, reduced design difficulty, and improved utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

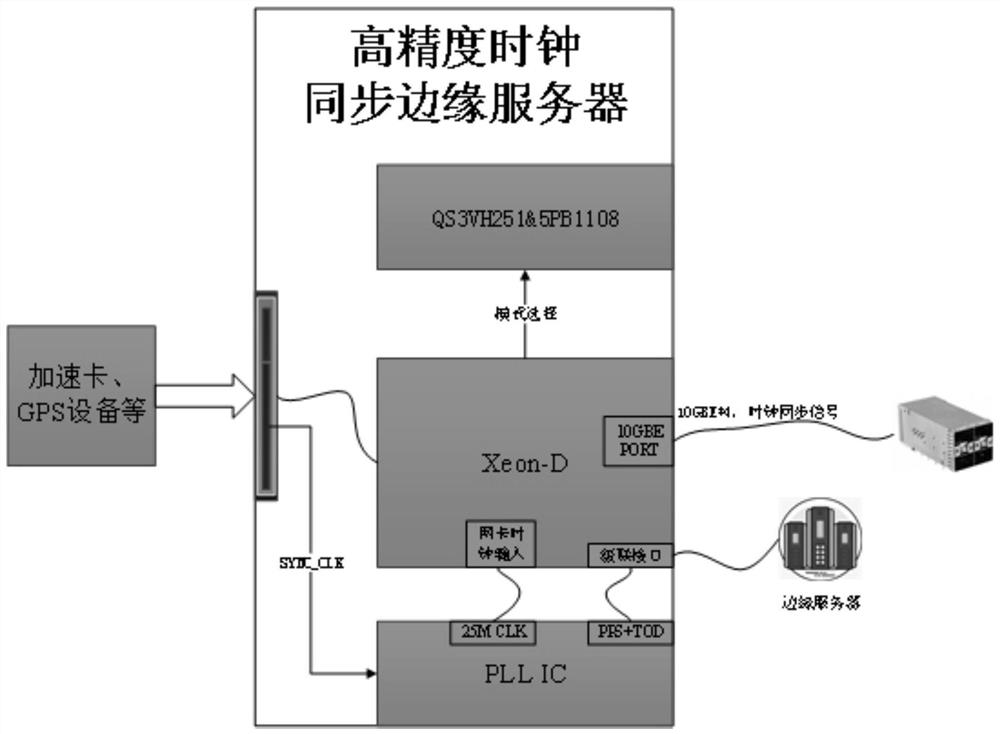

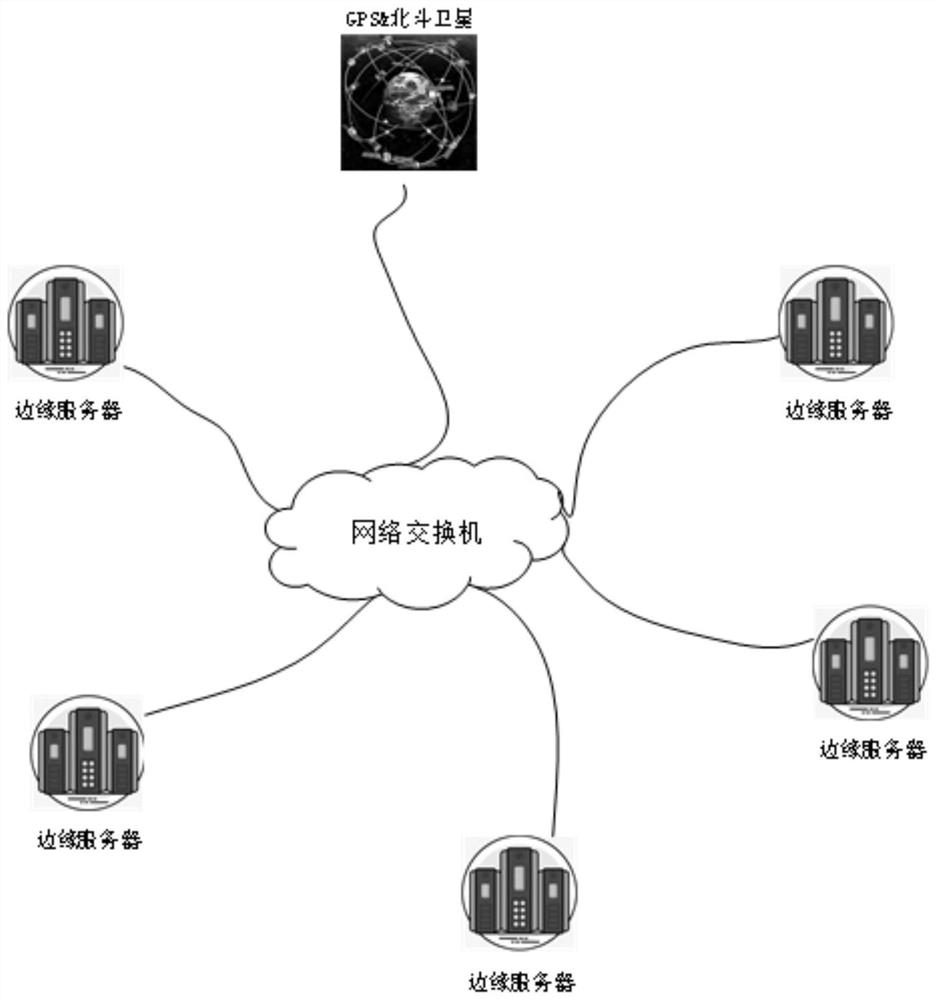

[0030] 1) The Xeon-D processor is selected as the processor of the edge server. The processor integrates the X722 network card, has four 10GBE ports, and has the clock synchronization function of IEEE 1588 mode, and the clock synchronization information can be obtained through the network.

[0031] 2) After the processor obtains the clock synchronization information on the network, it will perform clock synchronization processing, and transmit PPS+TOD information through PCIe links, I2C links, etc., to achieve clock synchronization inside the edge server, and at the same time use the processing more efficiently device.

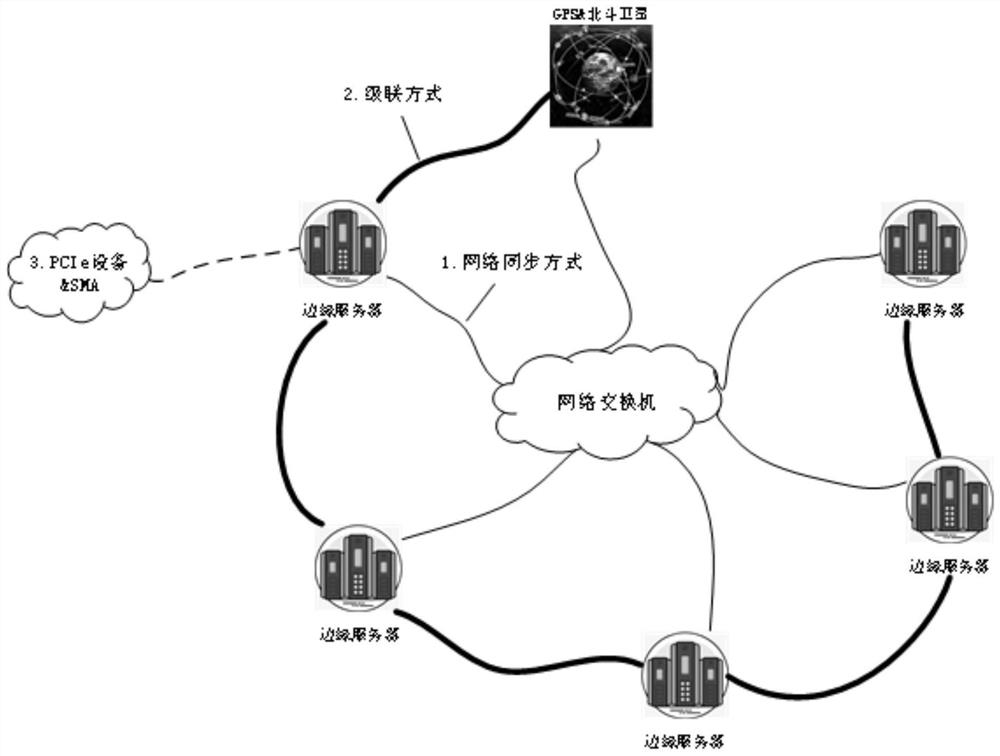

[0032] 3) When the external environment is relatively harsh and cannot obtain network information, such as desert, rainforest, subway and other environments, the edge server cascade method of different base stations can be used for clock synchronization; after one of the edge servers obtains the reference clock information, it is reserved by the server The int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More