High-speed Ethernet frame reconstruction system based on FPGA

A technology for reconstructing systems, Ethernet, applied in transmission systems, architectures with a single central processor, instruments, etc., can solve performance limitations, Ethernet small packets are difficult to reach wire speed, and cannot support nanosecond precision timestamp resolution. rate and other issues to achieve the effect of reducing overhead, low CPU usage, and improving system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

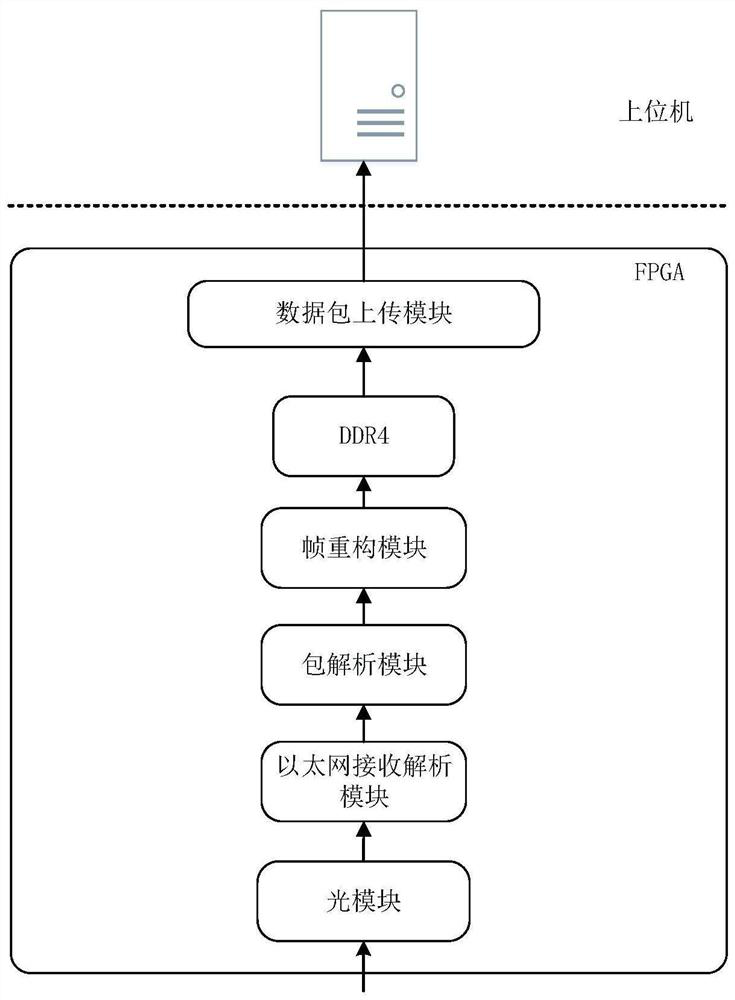

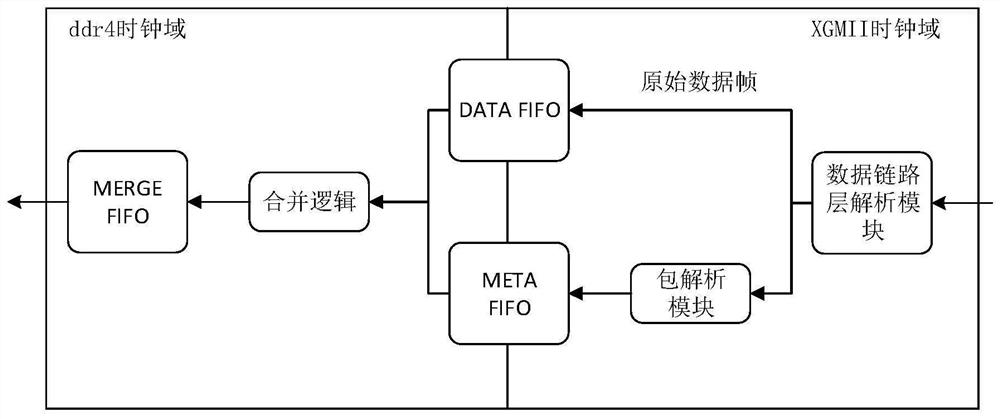

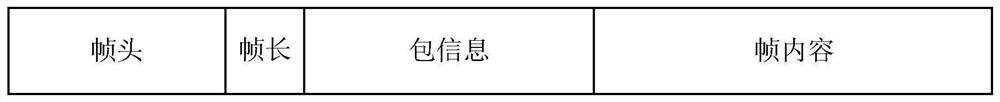

[0037] The invention proposes an FPGA-based frame reconstruction method, which offloads the high-speed network data packet processing function deployed on the server to the FPGA, utilizes its parallel characteristics, improves data packet processing performance, and reduces CPU load. This method uses hardware to parse out the data packet information and merges it into the original data frame, and then uploads it to the server memory through a high-speed DMA channel. The application on the server side can obtain the data packet information parsed in advance more easily and conveniently, and significantly improve the data packet processing performance. . By adopting the method of the present invention, it is possible to process the 10Gbps data packets of a single optical port at a wire speed, analyze the packet header information, and increase the time stamp of the data packet capture, quickly insert required bytes into the high-speed code stream, support jumbo frames, and The C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More