Capacitance-to-digital converter for eliminating parasitic based on SAR logic

A digital converter and capacitor technology, applied in the direction of analog/digital conversion calibration/test, physical parameter compensation/prevention, etc., can solve the problems of limited linearity and dynamic range of ADC capacitance-to-digital converter, and overcome the capacitance detection range. Contradictions with detection accuracy, high dynamic range, and the effect of improving capacitance detection range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

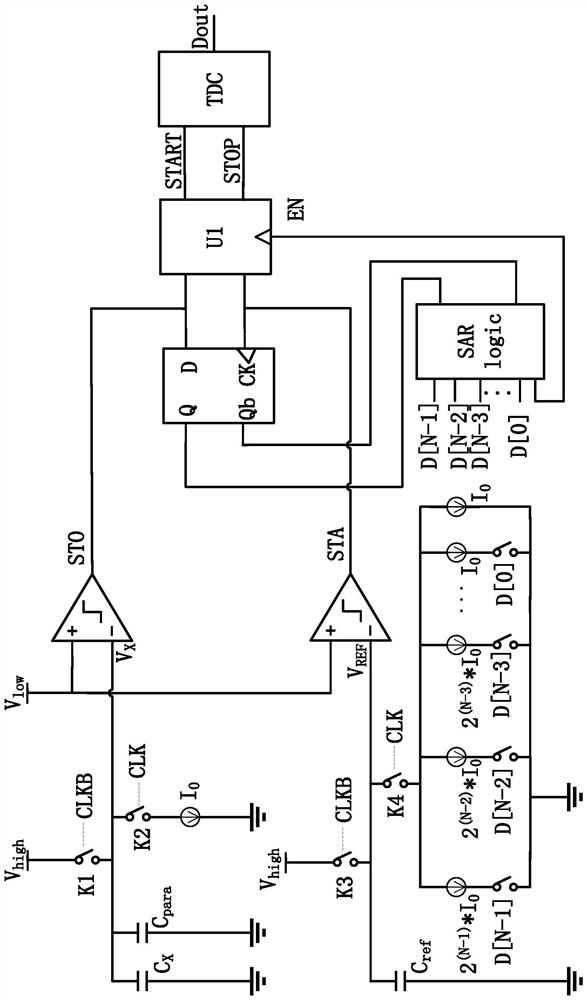

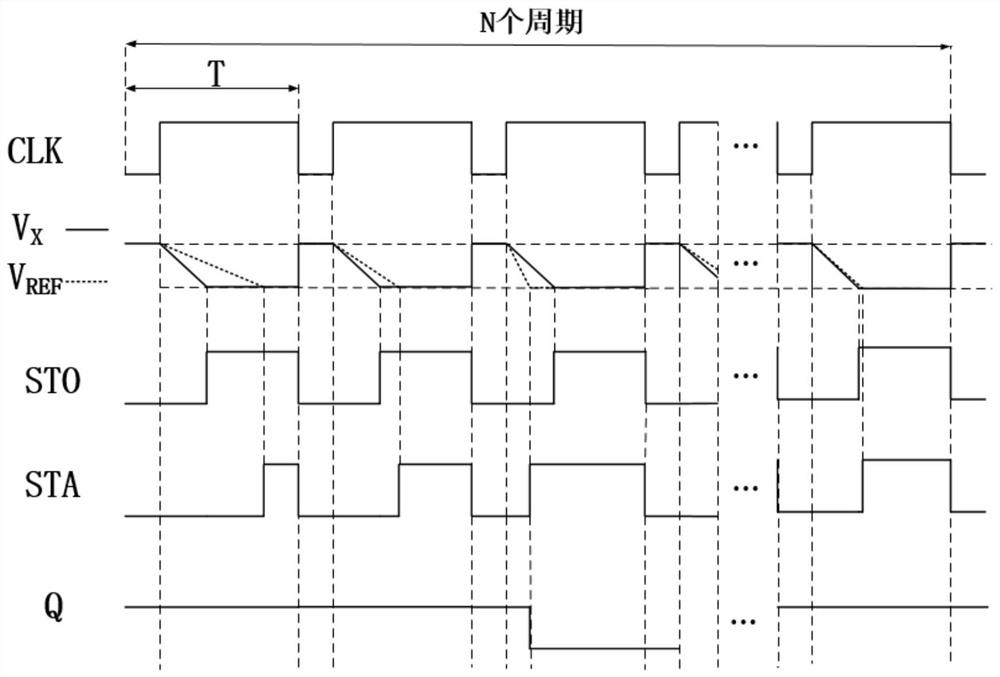

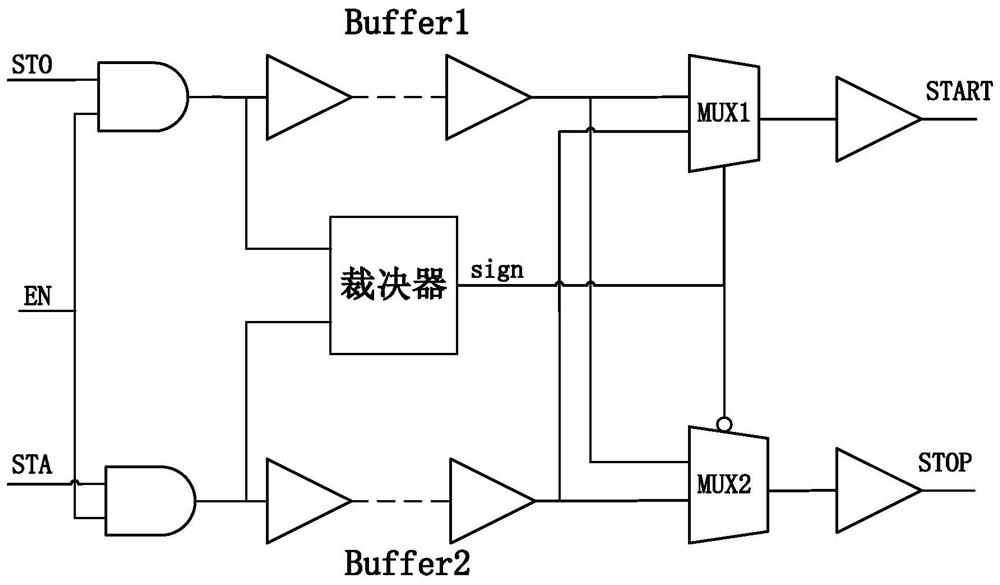

[0016]Such asfigure 1 As shown, a capacitance-to-digital converter based on SAR logic to eliminate parasitics according to the present invention includes a front-end CT conversion circuit electrically connected in sequence, a phase detector, a parasitic capacitance elimination circuit, a preprocessing logic module U1, and a time-to-digital converter .

[0017]The front-end C-T conversion circuit mainly includes two capacitor charging and discharging channels; the first channel charging and discharging structure includes the measured capacitor Cx, the parasitic capacitor Cpara, the switch K1, the switch K2, the first discharge current source and the first high-speed comparator. The negative terminal of the measured capacitance Cx and the parasitic capacitance Cpara is grounded, the positive terminal is connected to the drain terminal of switch K1 and switch K2 and the negative terminal of the first high-speed comparator, and the source terminal of switch K1 is connected to the reference...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More