High-precision clock synchronization method based on FPGA

A clock synchronization and clock technology, used in time division multiplexing systems, electrical components, multiplexing communications, etc., can solve the problems of increasing the size of user nodes, increasing R&D and debugging costs, and reduce the R&D cycle and cost. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary and are intended to explain the present invention and should not be construed as limiting the present invention.

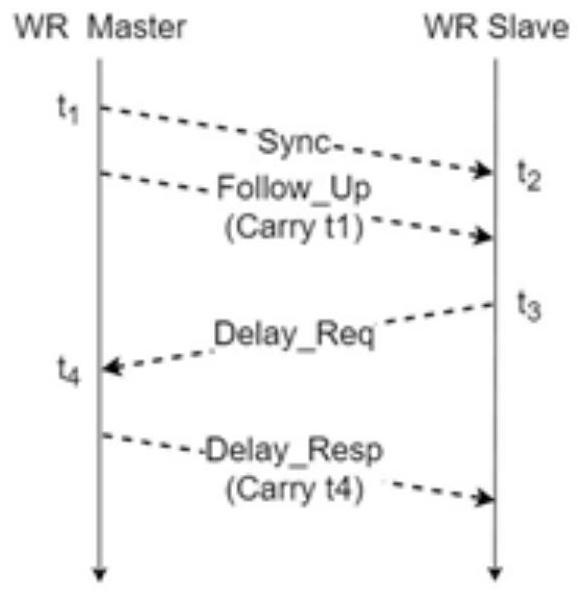

[0029] First of all, in the current related technical solutions, the WR high-precision clock synchronization network is a relatively mature solution. WR technology is an Ethernet-based high-precision clock synchronization solution proposed by CERN, which can achieve sub-nanosecond clock synchronization accuracy and tens of picosecond clock accuracy. The WR network is an open source project, and there are already many commercial companies that can provide WR equipment.

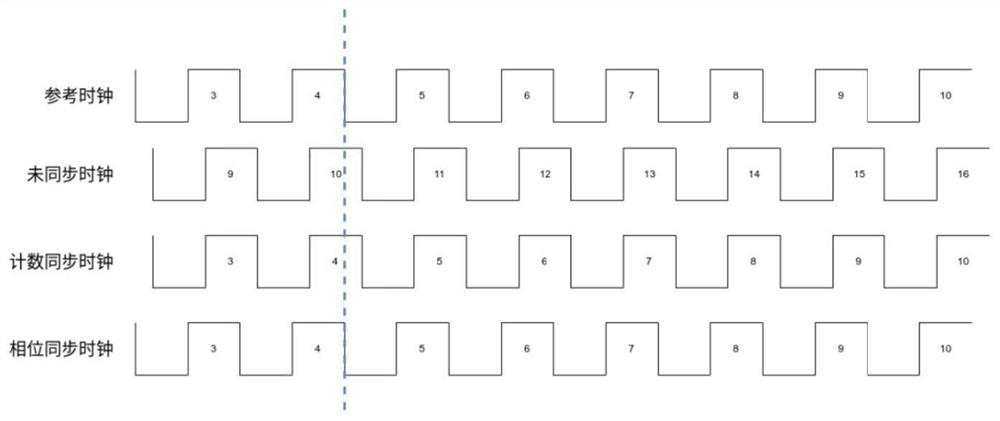

[0030] WR clock synchronization is divided into three steps...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More