Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as the influence of lithography alignment accuracy, Mesa width, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

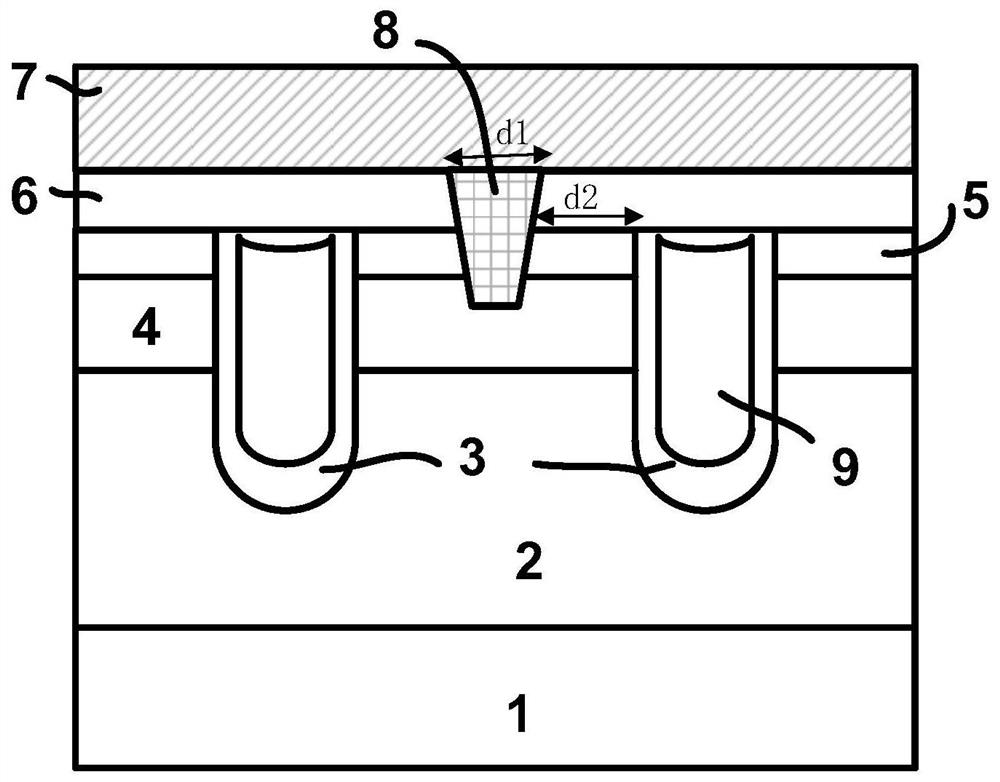

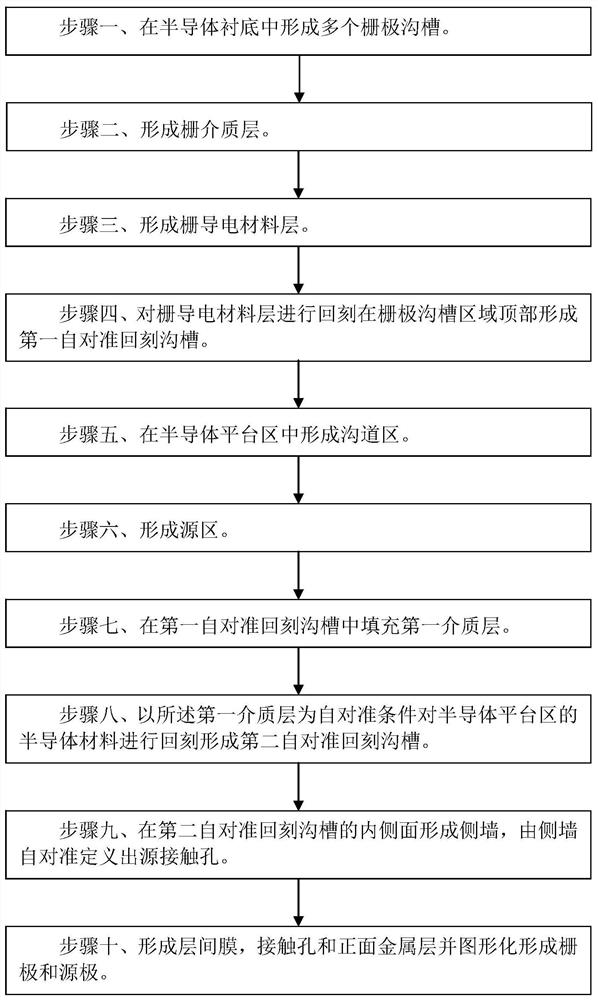

[0057] Such as figure 2 Shown is the flowchart of the manufacturing method of the semiconductor device of the first embodiment of the present invention; as Figure 3A to Figure 3I Shown is a schematic diagram of the device structure in each step of the manufacturing method of the semiconductor device according to the first embodiment of the present invention. The method for manufacturing a semiconductor device according to the first embodiment of the present invention includes the following steps:

[0058] Step 1, such as Figure 3A As shown, a semiconductor substrate 101 is provided, and the top surface of the semiconductor substrate 101 is a first surface; a plurality of gate trenches 201 are formed in the semiconductor substrate 101 by photolithography definition and etching process, and each phase The area between the adjacent gate trenches 201 is a semiconductor platform region; in the current flow region of a semiconductor device, a primitive cell is composed of one g...

no. 1 example approach

[0092] Take a semiconductor device with a breakdown voltage of 20V and a cell step of 0.5 microns, that is, the corresponding MOSFET device in the first embodiment of the present invention, as an example: for a low-voltage MOSFET, a highly doped phosphorus semiconductor substrate 101 is usually used , instead of using a highly doped arsenic semiconductor substrate, because the phosphorus-doped semiconductor substrate has a lower minimum resistivity than the arsenic-doped semiconductor substrate. At present, the resistivity of phosphorus-doped semiconductor substrates can be as low as 0.7mΩ*cm to 0.9mΩ*cm, while for arsenic substrates, the resistivity can be as low as 1.0mΩ*cm to 1.5mΩ*cm. Because of the low specific on-resistance of low-voltage devices, the substrate accounts for a large proportion of the total on-resistance, and lower substrate resistance becomes more important.

[0093] There is an epitaxial layer on the semiconductor substrate 101. In order to reduce the re...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More