Trench gate MOSFET device and manufacturing method thereof

A trench gate and device technology, applied in the manufacture of trench gate MOSFET devices, in the field of trench gate MOSFET devices, can solve problems such as the influence of lithographic alignment accuracy and Mesa width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0064] Trench gate MOSFET device of the first embodiment of the present invention:

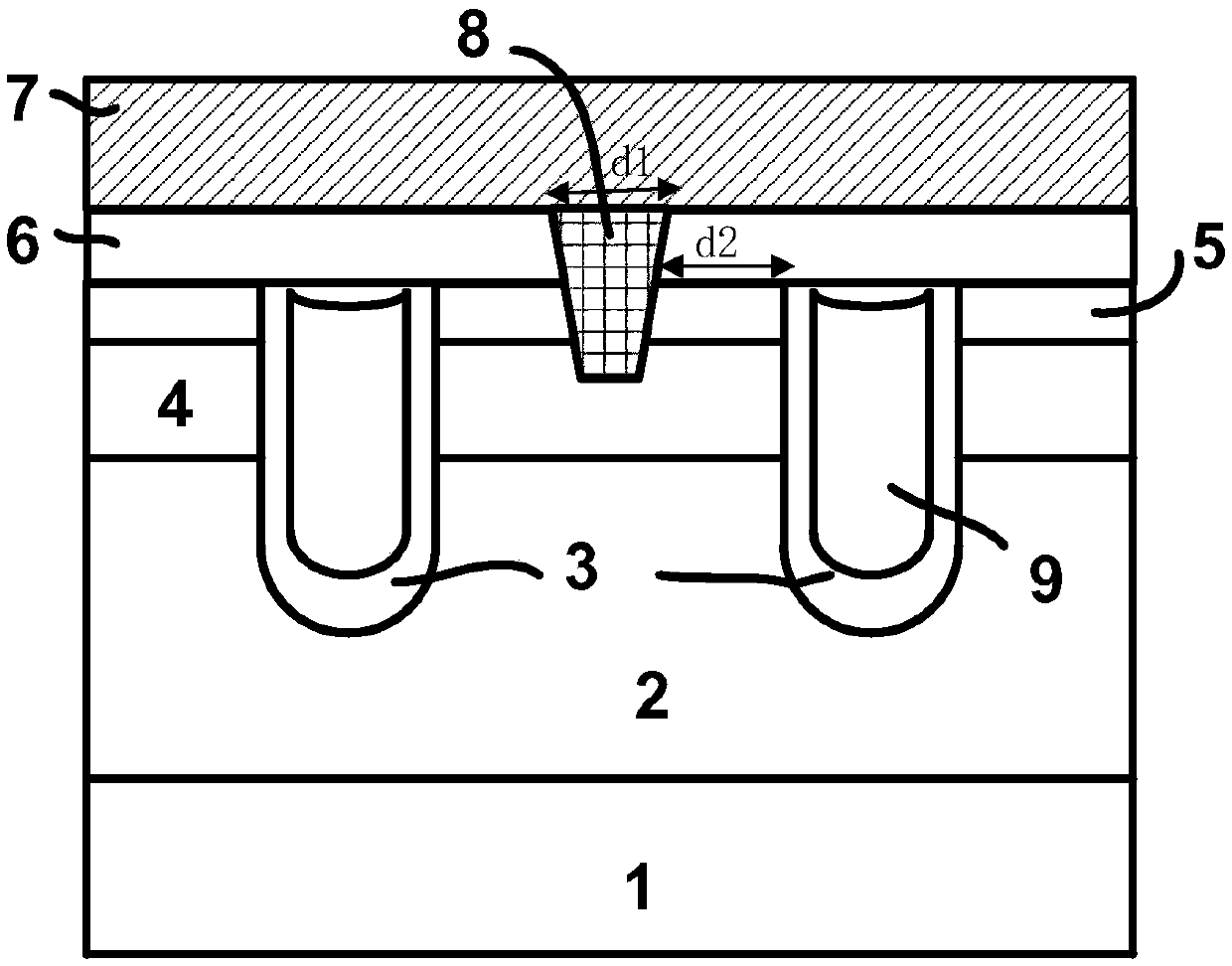

[0065] Such as figure 2 Shown is a schematic structural diagram of a trench gate MOSFET device in the first embodiment of the present invention. The trench gate MOSFET device in the first embodiment of the present invention is formed in a semiconductor substrate 101, and the top surface of the semiconductor substrate 101 is the first Surface: the current flow area of the trench gate MOSFET device is composed of a plurality of primitive cells arranged periodically, and the trench gate of each primitive cell includes a gate trench 201 , a gate dielectric layer 102 and a gate conductive material layer 103 .

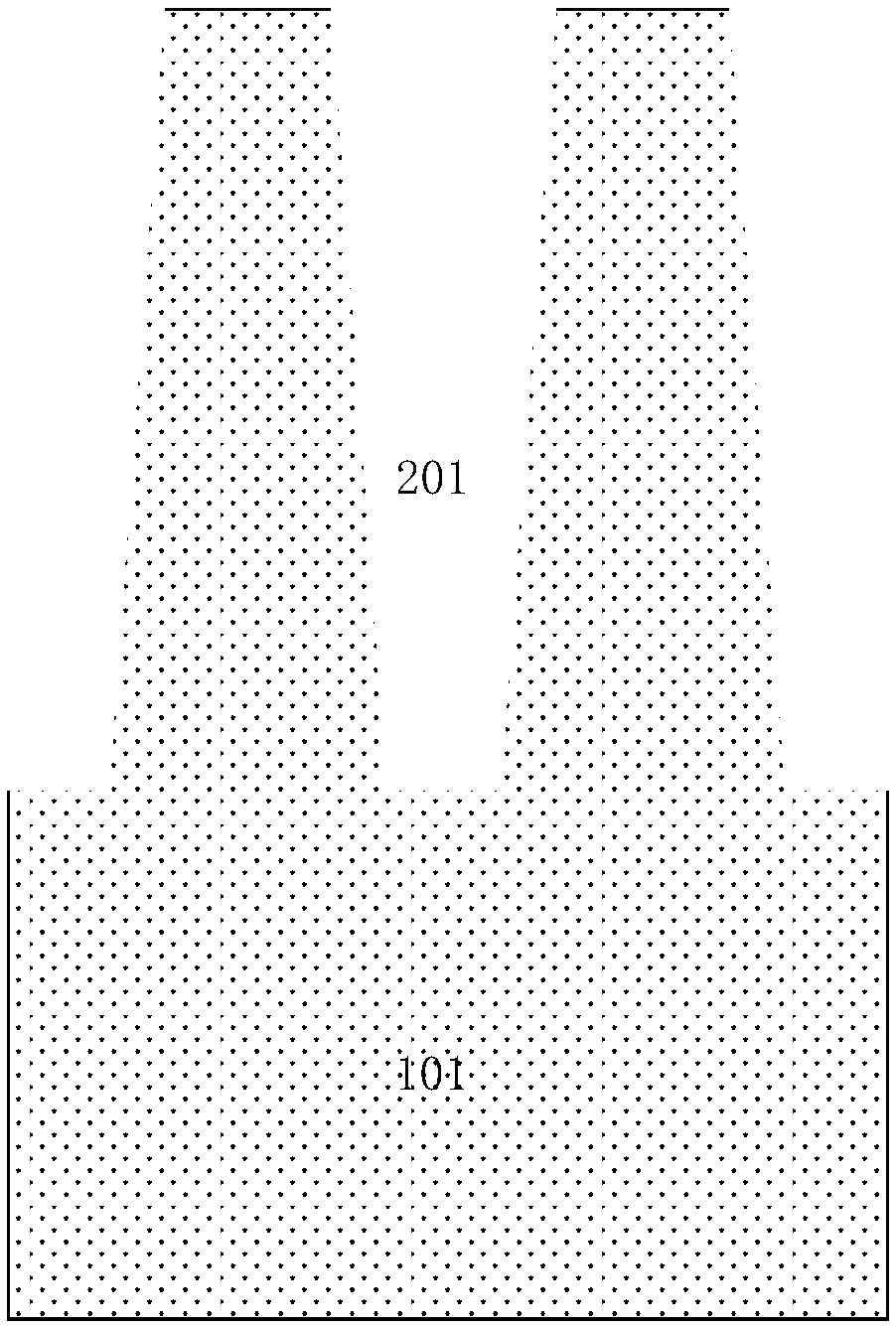

[0066] The gate trenches 201 are formed in the semiconductor substrate 101 , and the regions between adjacent gate trenches 201 are semiconductor platform regions.

[0067] The gate dielectric layer 102 is formed on the bottom surface and side surfaces of the gate trench 201 , and the ga...

no. 1 example

[0081] In order to illustrate the device of the first embodiment of the present invention more clearly, the device of the first embodiment of the present invention is further described in conjunction with specific parameters:

[0082] For a 20V trench gate MOSFET device, a highly doped phosphorus semiconductor substrate 101 is usually used, the resistivity of the semiconductor substrate 101 is 0.0011Ω*cm, and the thickest thickness of the semiconductor substrate 101 after thinning is 150 μm. Usually, a semiconductor epitaxial layer, such as a silicon epitaxial layer, is further formed on the surface of the semiconductor substrate 101 , and the trench gate is formed in the semiconductor epitaxial layer. The semiconductor epitaxial layer is a single-layer epitaxial layer, the resistivity of the epitaxial layer is 0.15Ω*cm, and the thickness of the epitaxial layer is 4 μm. The gate trench 201 of the trench gate MOSFET device has a width of 0.2 μm.

[0083] The opening of the ga...

no. 2 example

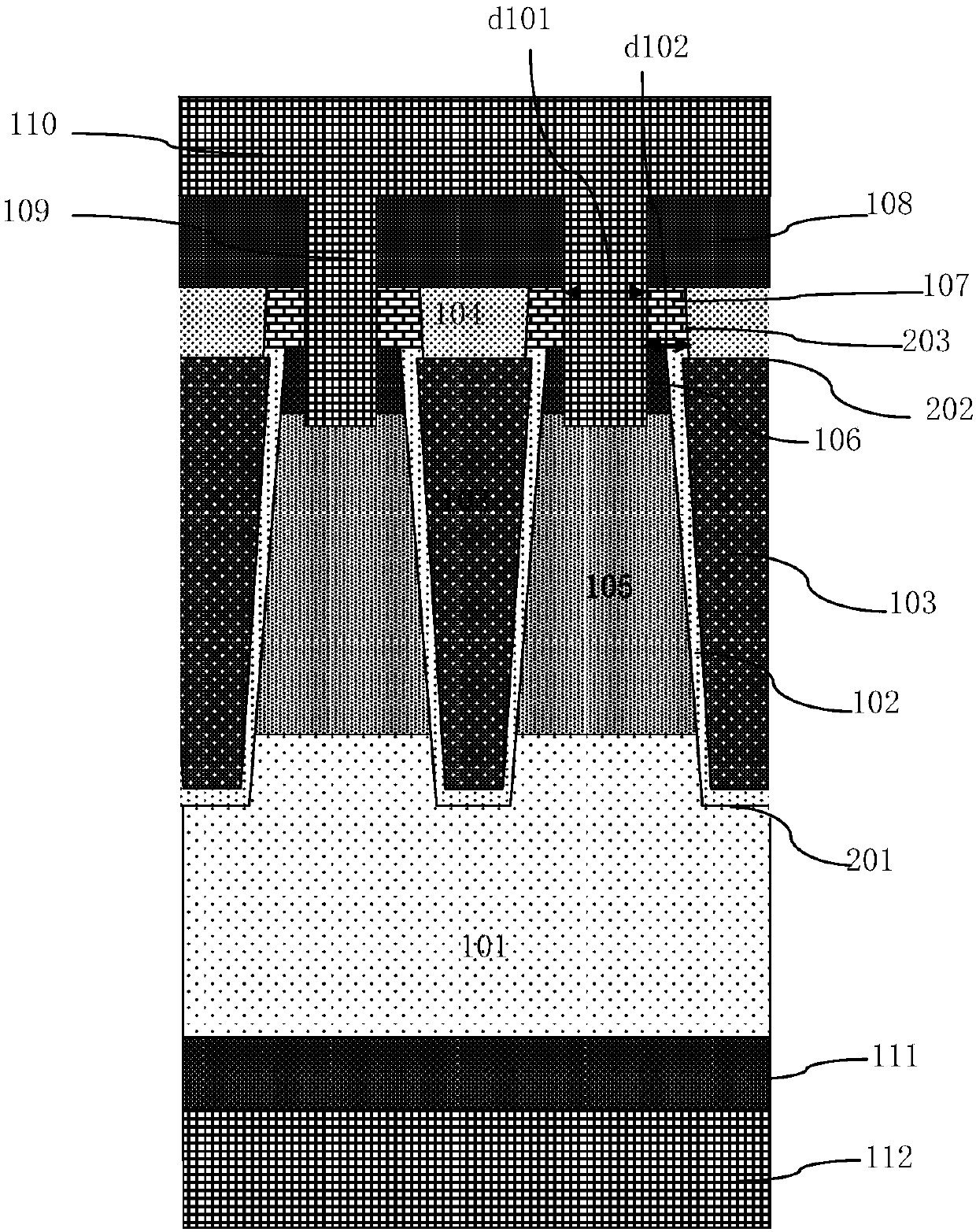

[0093] Trench gate MOSFET device of the second embodiment of the present invention:

[0094] The difference between the device of the first embodiment of the present invention is that the trench gate MOSFET device of the second embodiment of the present invention has the following features:

[0095] The trench gate MOSFET also has a shielding layer, which is an SGT MOSFET, and the shielding layer is formed in the gate trench 201 at the bottom of the gate conductive material layer 103, and the material of the shielding layer is conductive to the gate. The materials of the material layer 103 are the same, a shielding medium layer is isolated between the shielding layer and the bottom surface and side surfaces of the gate trench 201, and a gate gap is separated between the shielding layer and the gate conductive material layer 103. Isolated dielectric layer.

[0096] In fact, for SGT MOSFETs, reducing the width of Mesa is more meaningful. This is because for SGT, the shielding ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More