STT-MRAM-based multi-channel high-speed data access structure

A high-speed data, multi-channel technology, applied in data conversion, electrical digital data processing, instruments, etc., can solve the problems of low memory access efficiency, high power consumption overhead, complex control logic, etc., to achieve simple control logic and low power consumption Low, the effect of improving the overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

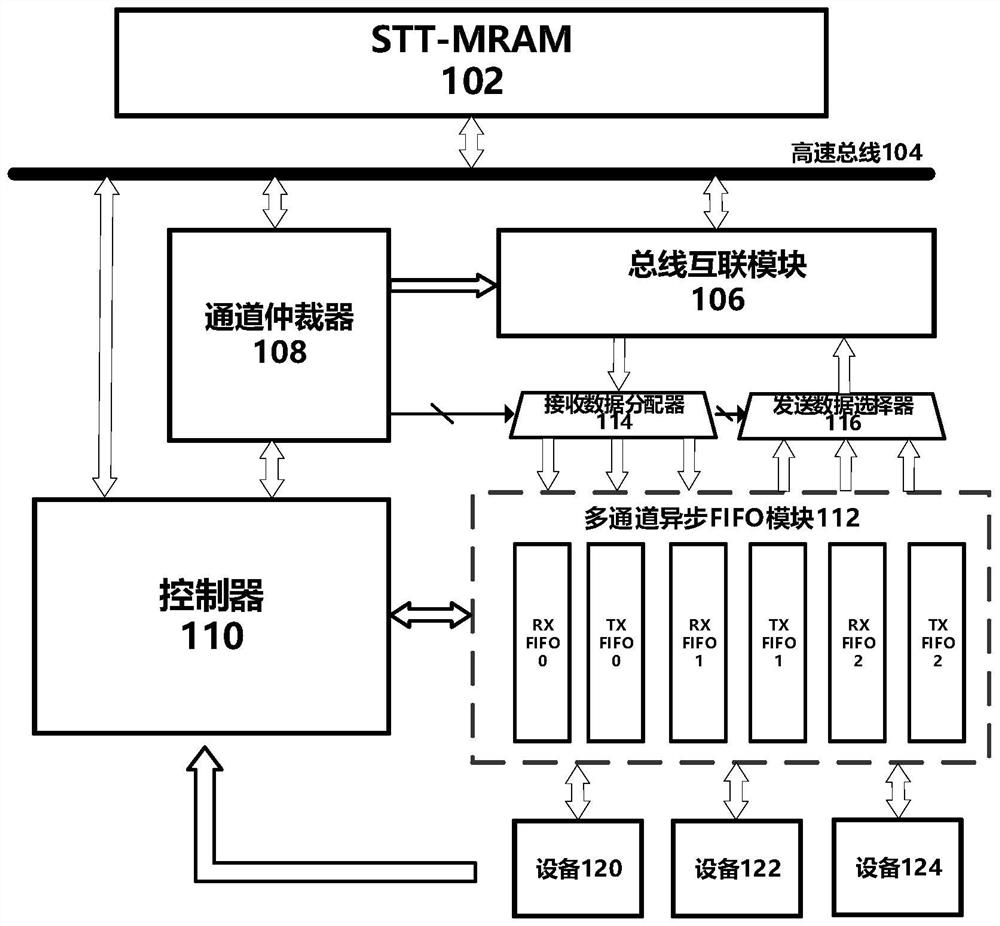

[0022] In order to make full use of the high-performance characteristics of the new memory STT-MRAM and realize high-speed data access suitable for various application scenarios, the present invention provides a multi-channel high-speed data access circuit structure based on STT-MRAM, such as figure 1 As shown, it includes: STT-MRAM 102 with a bus interface, a high-speed bus 104 , a bus intercon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More