An error recovery method for multiprocessor chips based on three-mode lockstep

An error recovery and multi-processor technology, applied in the computer field, can solve the problems of undetected and undetermined hard errors, and achieve the effects of reducing resource consumption, improving reliability and real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

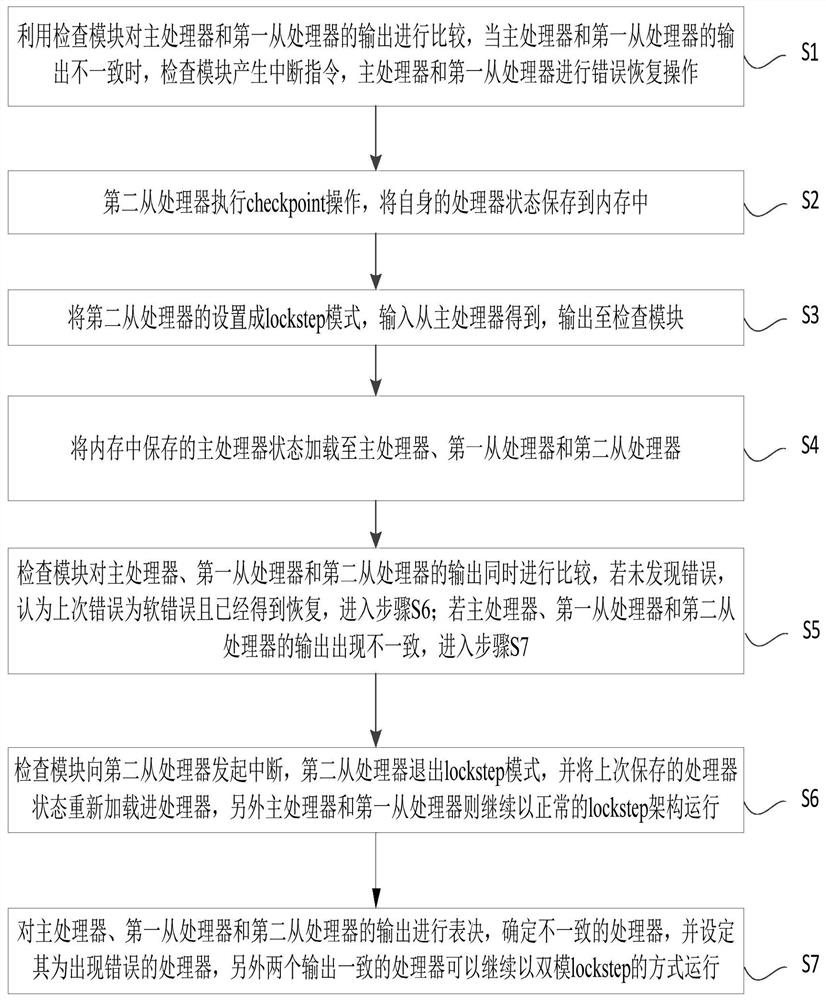

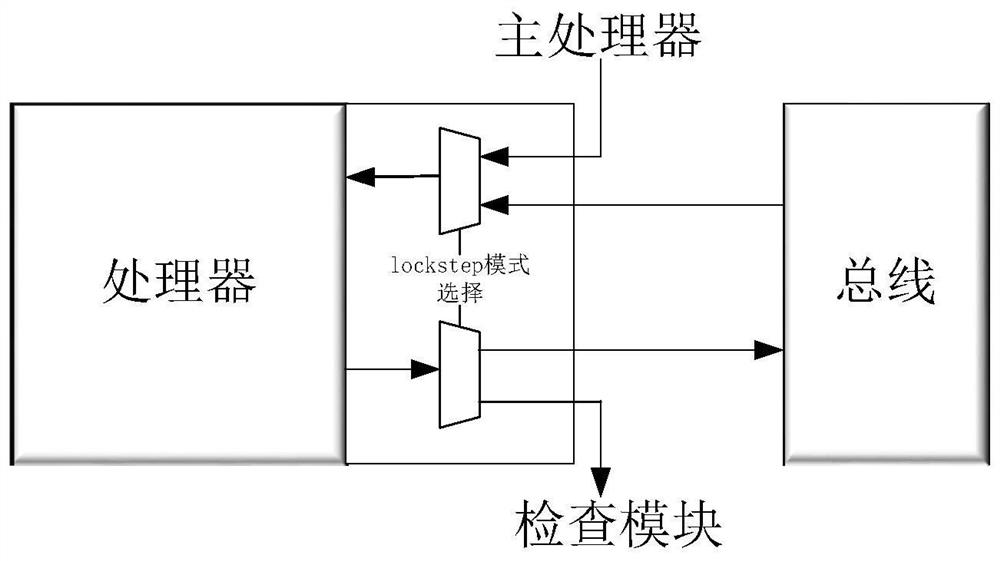

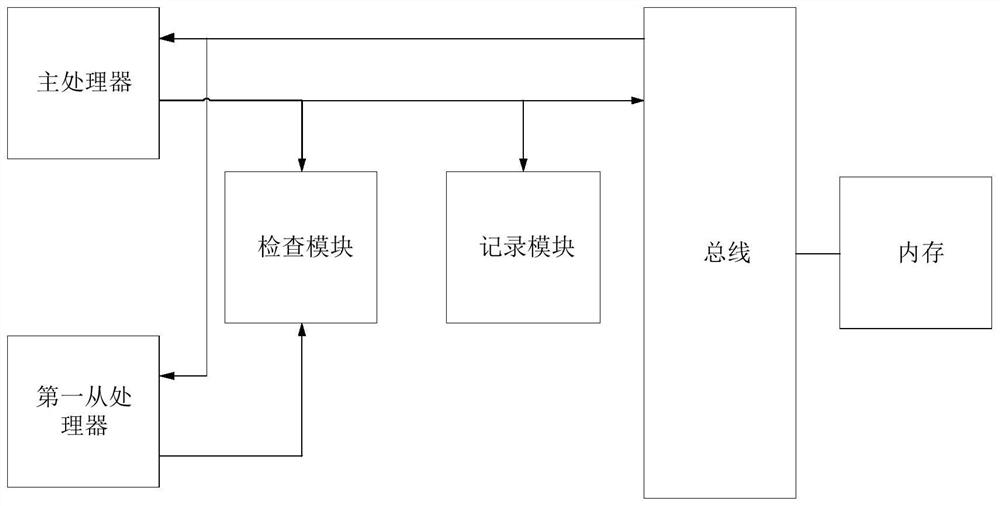

[0038] This embodiment provides a multi-processor chip error recovery method based on three-mode lockstep, such as Figures 1 to 4 , including the following steps:

[0039] S1: Use the check module to compare the outputs of the master processor and the first slave processor. When the outputs of the master processor and the first slave processor are inconsistent, the check module generates an interrupt instruction, and the master processor and the first slave processor perform error recovery operations;

[0040] S2: The second slave processor executes the checkpoint operation, and saves its own processor state into the memory;

[0041] S3: Set the second slave processor to lockstep mode, the input is obtained from the main processor, and the output is sent to the inspection module;

[0042] S4: loading the main processor state saved in the memory to the main processor, the first slave processor and the second slave processor;

[0043] S5: The checking module compares the out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More