Triplication redundancy method based on molecular-level netlist

A three-mode redundant, molecular-level technology, applied in the field of FPGA, can solve problems such as SRAM interference and SRAM failure, and achieve the effect of convenient verification, low cost and easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

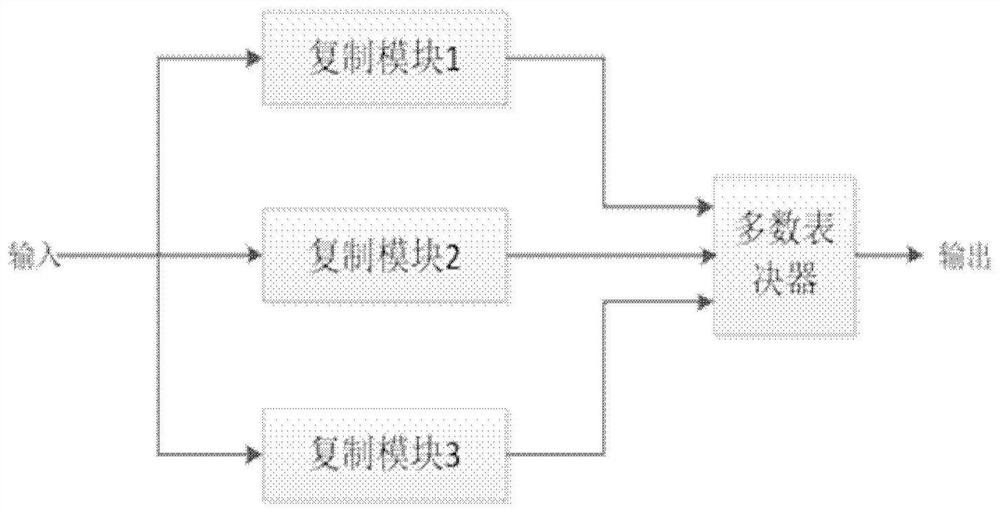

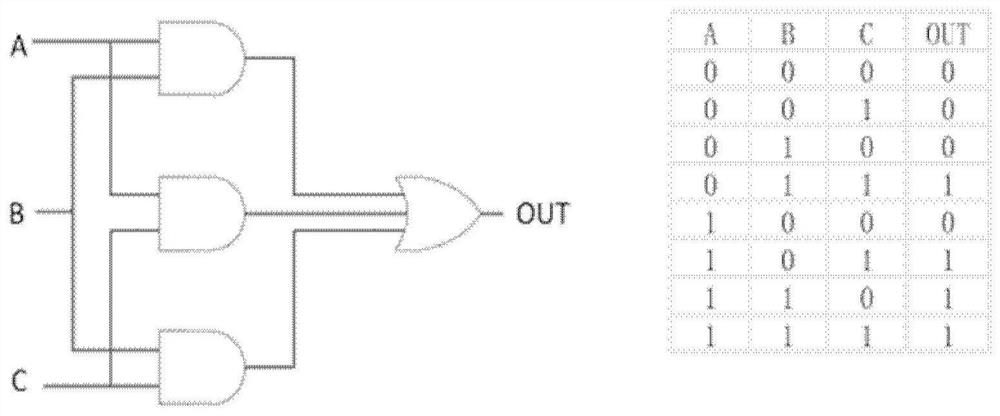

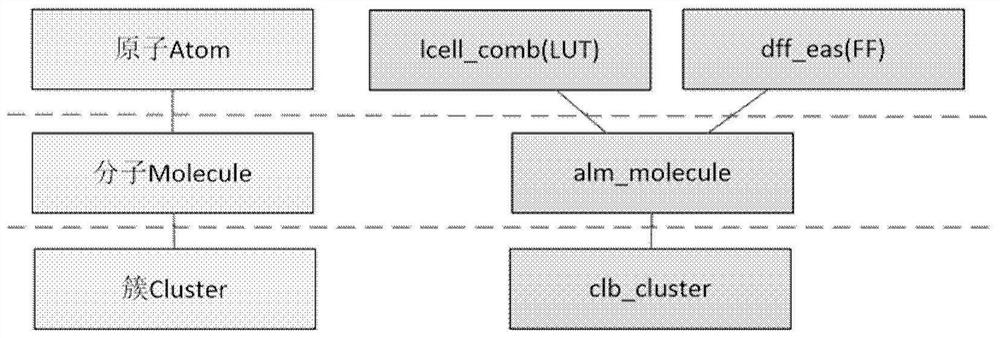

[0033] The present disclosure provides a triple-module redundancy method based on a molecular-level netlist, which uses the user-designed and synthesized netlist file as an output to perform molecular-level TMR (Triple Module Redundancy, triple-mode redundancy), effectively controlling resource consumption. At the same time, the reliability of the device is guaranteed.

[0034] During the process of realizing the present disclosure, the inventors found that the single event upset protection technology of FPGA can be divided into hardware protection and software protection.

[0035] Hardware protection refers to increasing the fault tolerance of the system through hardware design. The main technologies include power cycle, static refresh, dynamic refresh (configuration management), and device redundancy. Hardware protection has high reliability but high cost, and is suitable for working conditions with a high probability of SEU (Single Event Upset, single event upset effect). ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More