FPGA hardware implementation method and device based on Bayesian resampling particle filtering and a target tracking method

A technology of particle filtering and hardware implementation, applied to digital computer components, architecture with a single central processing unit, instruments, etc., can solve problems such as low parallelism of multi-core CPUs, limited speed-up ratio, time waste, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The following is a detailed description of the embodiments of the present invention. This embodiment is carried out based on the technical solution of the present invention, and provides detailed implementation methods and specific operation processes to further explain the technical solution of the present invention.

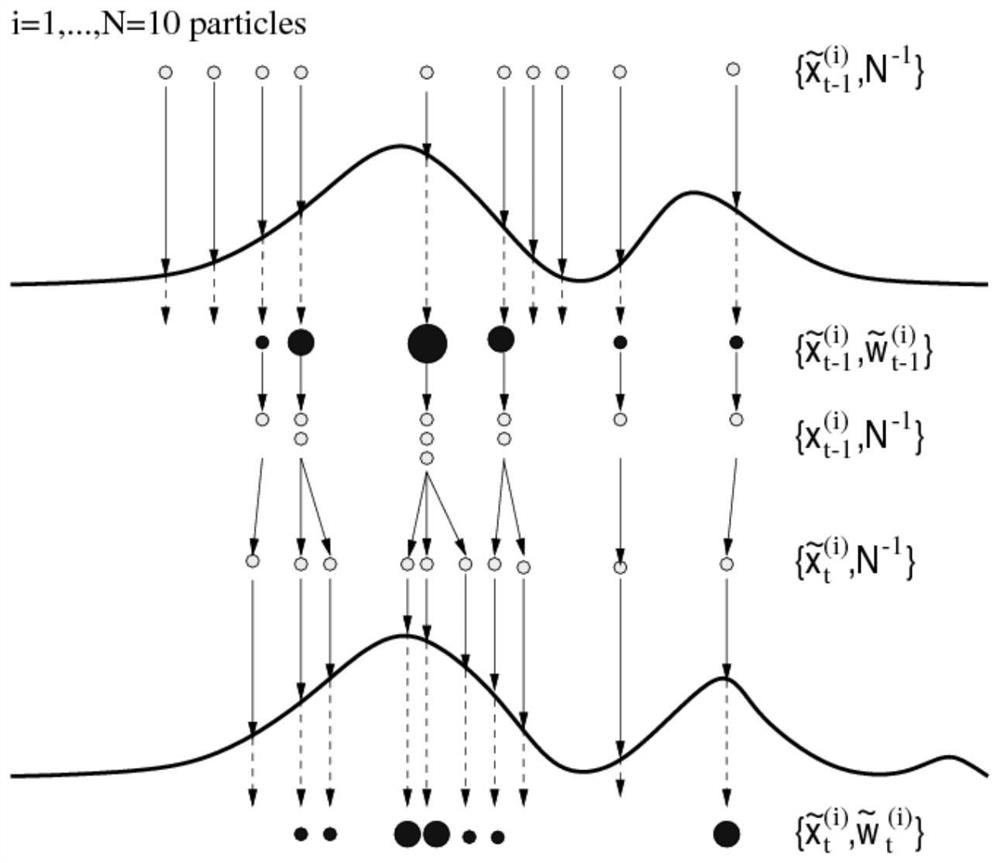

[0028] The embodiment of the present invention provides a kind of FPGA hardware implementation method based on Bayesian resampling of particle filtering, wherein FPGA such as Figure 4 As shown, including: a calculation module, a pseudo-random permutation generator, n random number generators, n particle cache blocks, n weight cache blocks, n index cache blocks and observation value cache blocks, the calculation module includes There are n particle sampling units, n weight updating units and n Bayesian resampling units in one-to-one correspondence between input and output; the FPGA hardware implementation method specifically includes the following steps: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More