Coarse-grained dynamic reconfigurable processor and data processing method thereof

A data processing and processor technology, applied in the direction of electrical digital data processing, architecture with a single central processing unit, instruments, etc., can solve the problems that cannot satisfy general hardware programming flexibility, high computing performance and high energy efficiency at the same time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

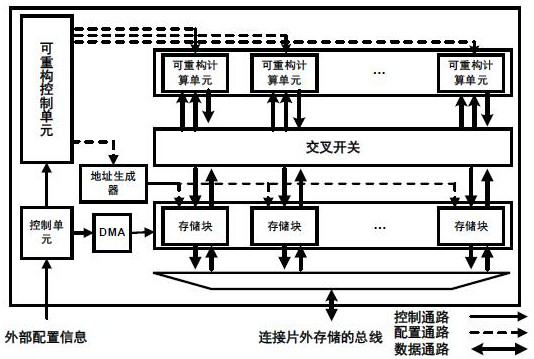

[0060]This example discloses a common coarse granular dynamic reconfigurable processor in the field, and is schematically shownfigure 1 As shown, the processor includes the following main unit: control unit; reconstructing control unit; reconstructing calculation array; on-chip storage pool consisting of plurality of sheets, generating the memory block accessed address, no conflict address Generator; Direct Memory Access (DMA) module and data distribution module between the DMA and the storage pool.

[0061]The relationship between the main units is as follows: The control unit transmits the parsed configuration information to the reconstructed control unit; the reconstructed control unit generates all the selection in the reconfigurable calculation array according to the configuration information. The selection signal of the passage completes the reconstruction of the calculation array; the reconstructed calculation array is written according to the address generated by the unstuffed ...

Embodiment 2

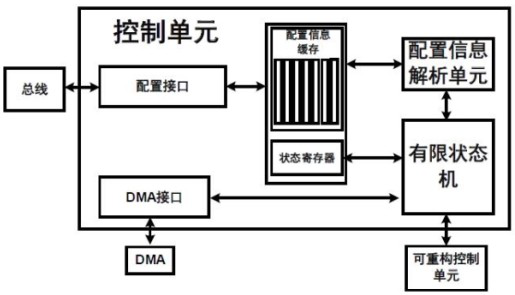

[0063]On the basis of the first example, the architecture of the control unit is schematicallyfigure 2 As shown, it mainly includes the following main unit: configuring an interface, configuration information cache, configuration information parsing unit, a finite state machine, a DMA control interface, a status register, and the like. The relationship between the main units is as follows: The reconstructed processor disclosed herein is actively or passively received external configuration information by a configuration interface; when in the configuration information prefetch mode, the configuration interface will be deposited. In the configuration information cache; the configuration information parsing unit reads the configuration information from the configuration information cache, then decomposes the multi-stroke configuration word, and then analyzes the bit domain meaning of the agreed configuration information, first perform parsing of the fixed sense sub-configuration word,...

Embodiment 3

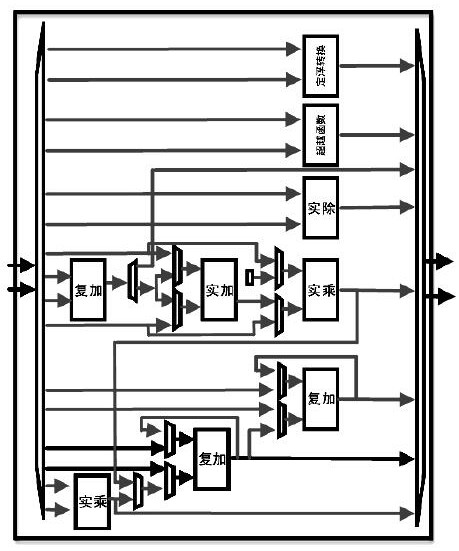

[0065]On the basis of the first or embodiment 2, the operator is mapped to the reconfigurable calculation array.image 3 ,Figure 4 ,Figure 5 Indicated. Reconfigurable calculation arrays are interconnected by reconfigurable computing units, whereinimage 3 withFigure 4 It is a single reconfigurable compute unit. The reconfigurable computing unit includes several basic calculation components, in the present embodiment, including complex multiplication, plural addition, real multiplication, real number division, and other, including the selection path between these calculation components, can therefore Different functions can be achieved by different gathers for selecting pathways, such asimage 3 As shown, the complex function is realized by the gate, such asFigure 4 As shown, the plurality of multiplication capabilities of water-saving is achieved by gating. For more complex operators, the resource of a single reconfigurable compute unit cannot complete the mapping, and can be implement...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More