Interconnection die interface management system and initialization method thereof

An initialization method and interface management technology, applied in the field of bare core interface management, which can solve the problems of time-consuming reconstruction, difficult design, and complex process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

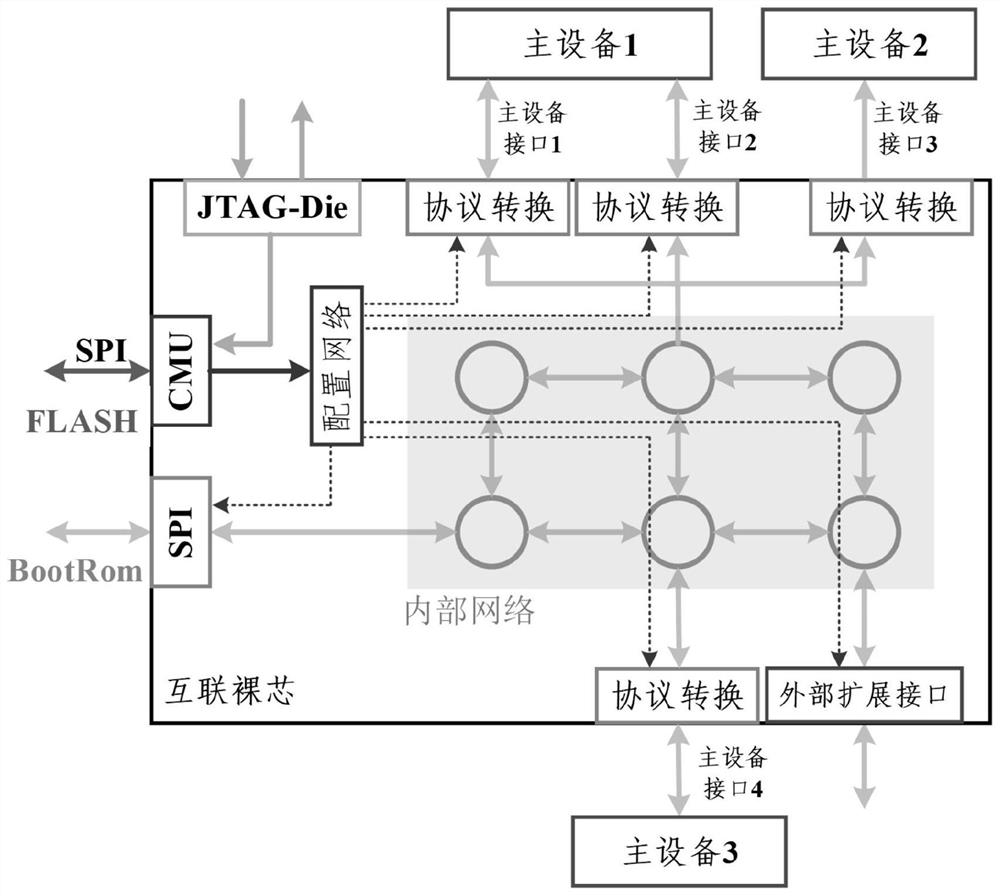

[0038] Such as figure 1As shown, the interconnected bare-core interface management system includes: a CMU system, a JTAG-Die interface and a configuration network that are all connected to the CMU system; the CMU system includes a CMU processor and a Flash connected to the CMU processor, and the Flash is used to store the software code of the CMU system; the JTAG-Die interface is used to control the startup of the CMU program; one end of the configuration network is connected to the CMU processor in the form of a peripheral, and the other end is connected to each interface to be configured through an independent bus ; When the CMU processor is used to execute its configuration program, the configuration data is transmitted to the function register of each interface to be configured through the configuration network and an independent bus, so as to realize the configuration of the interface address translation table.

[0039] The interconnect die interface management system is ...

Embodiment 2

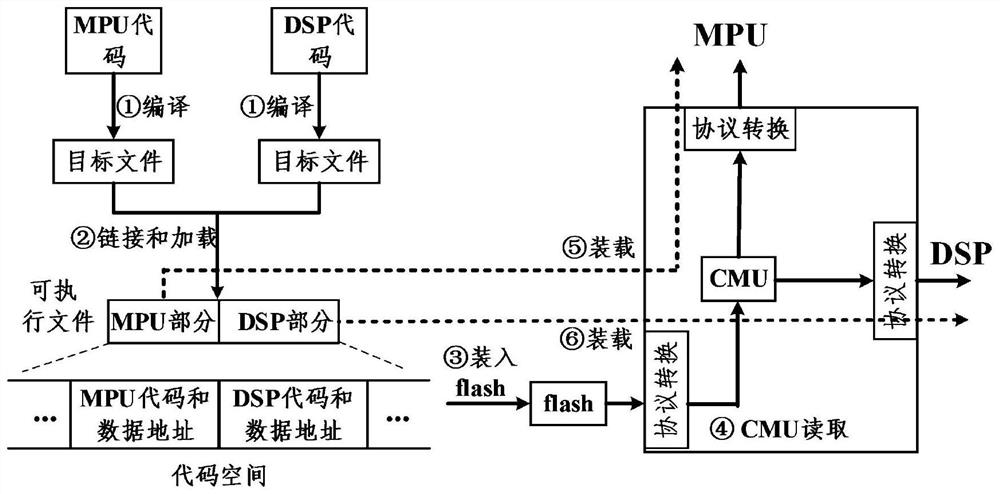

[0045] Such as figure 2 As shown, the initialization method of the interconnection bare core interface management system includes the following steps:

[0046] S101, respectively compiling the program codes of each master device to generate an object file;

[0047] S102, linking the target file with the startup code provided by the system through a linker to generate an executable file, loading the executable file into a designated code space, respectively corresponding to each master device code address space, and unified management by the CMU system;

[0048] S103, loading the codes and data addresses of each master device in the code space into the program memory Flash of the CMU system respectively;

[0049] S104, start the CMU system through the JTAG-Die interface, load and execute the program in the Flash, generate control signals for each protocol conversion interface, and configure it;

[0050] S105, each master device sequentially reads and executes the startup cod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More