Design method of miniaturized focal plane array test data acquisition and display system

A focal plane array and test data technology, which is applied in CAD circuit design, computer aided design, electrical digital data processing, etc., can solve problems such as difficult maintenance, unfavorable real-time display of focal plane array data, and difficult development, so as to simplify operation , to achieve the effect of collection and real-time display

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0023] The invention provides a method for designing a miniaturized focal plane array test data acquisition and display system, comprising the following steps:

[0024] Carry out the focal plane array test data acquisition and display system design according to steps S1-S4,

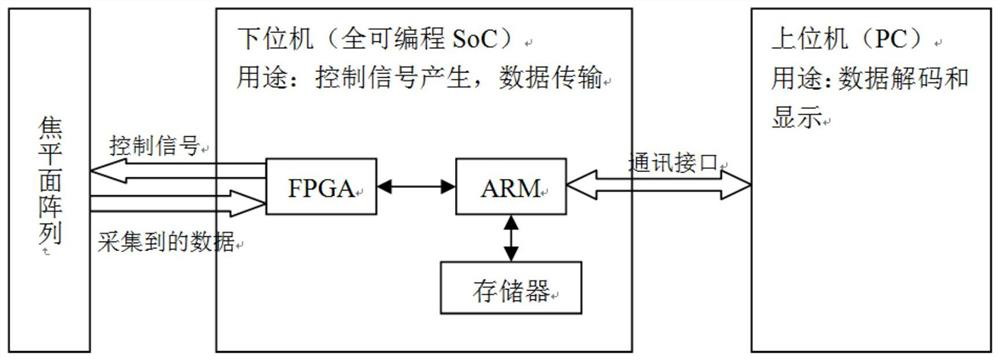

[0025] S1, determine the overall structure of focal plane array test data acquisition and display system, in the present invention, adopt computer as upper computer, fully programmable SoC circuit board as lower computer, and make the hardware housing of system;

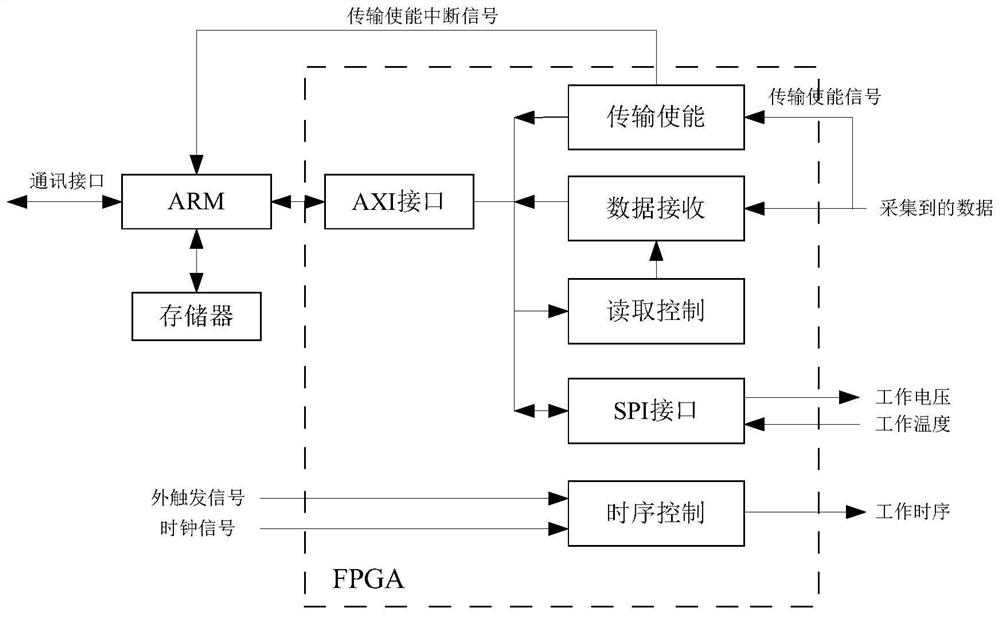

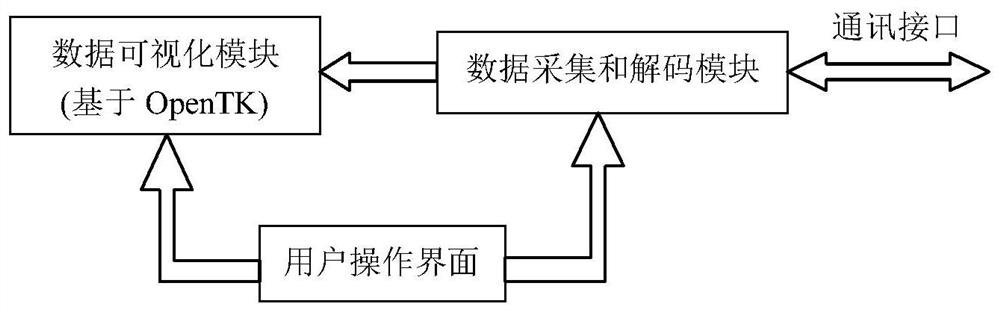

[0026] S2. In the lower computer, perform digital logic design on the FPGA part of the SoC chip, provide the working timing required by the focal plane array and collect the data obtaine...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More