Control circuit applied to pseudo static random access memory and control method thereof

A pseudo-static random access memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of short pulse width, pseudo-static random access memory failure, etc., achieve high operating frequency, avoid failure or Unstable operation, avoiding the effect of too short pulse width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

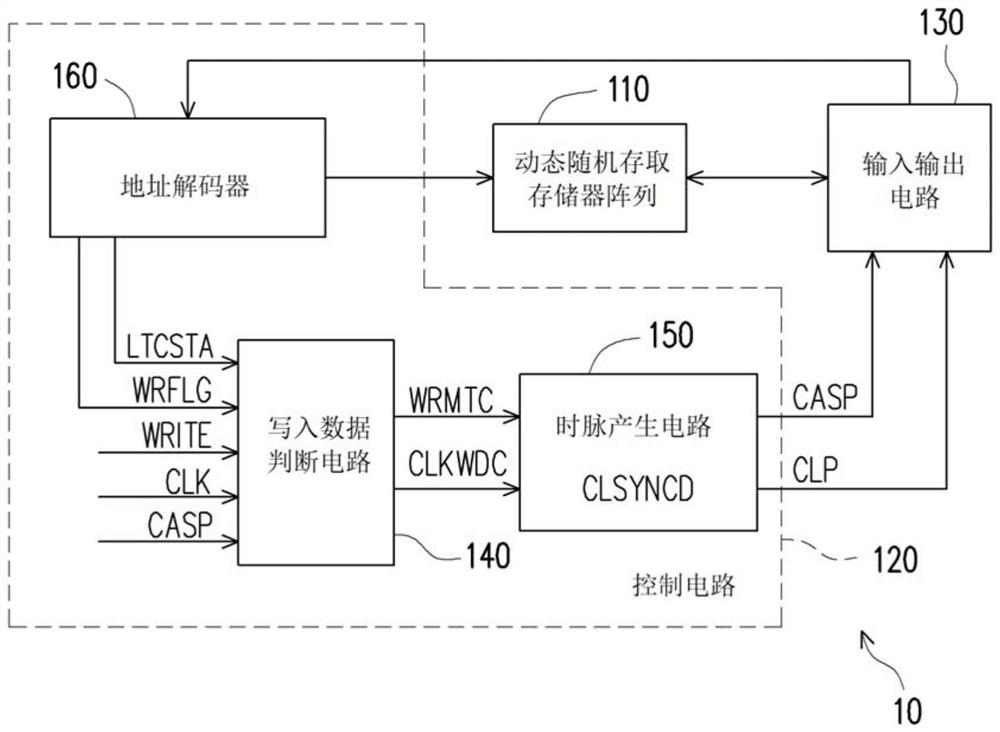

[0076] Please refer to figure 1 , figure 1 is a schematic diagram of a pseudo-static random access memory 10 according to an embodiment of the present invention. The pseudo-SRAM 10 includes a DRAM array 110 , a control circuit 120 , and an input-output circuit 130 . The DRAM array 110 includes a plurality of word lines and a plurality of memory cells (not shown) for storing data, and the present invention does not limit the architecture of the DRAM array. The control circuit 120 is coupled to the DRAM array 110 , and the control circuit 120 includes a write data determination circuit 140 , a clock generation circuit 150 and an address decoder 160 . The address decoder 160 is coupled to the write data judging circuit 140, the DRAM array 110, and the I / O circuit 130. The address decoder 160 can generate a counting start signal LTCSTA and a write flag signal WRFLG corresponding to the execution operations, and The count start signal LTCSTA and the write flag signal WRFLG are p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More