High-energy-efficiency on-chip memory error detection and correction circuit and implementation method

An on-chip memory and error detection technology, applied in error detection/correction, redundant code error detection, static memory, etc., can solve the problems of increasing microprocessor area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

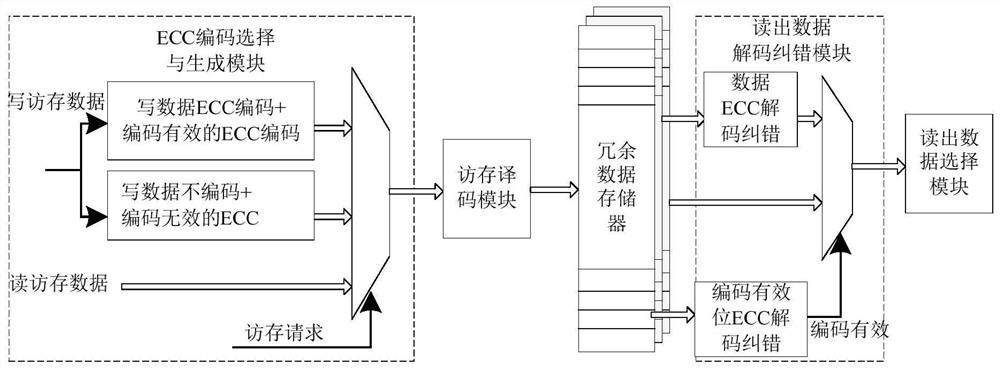

[0037] Such as figure 1 As shown, the energy-efficient on-chip memory error detection and error correction circuit of the present invention, according to the memory access process, includes:

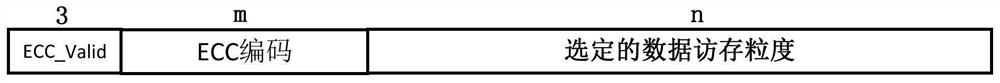

[0038] The ECC encoding selection and generation module is used to determine whether to perform ECC encoding according to the information in the access request issued by the access operation, perform ECC encoding on the effective bits of the ECC encoding of the access data, and combine the access information and related ECC encoding results Send it to the subsequent memory access decoding module;

[0039] A memory access decoding module and a redundant data memory, the memory access decoding module is used to perform memory access decoding according to read and write requests and memory access addresses, and generate redundant data memory memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More