MCU verification method and system and terminal equipment

A verification method and technology to be verified, applied in the field of system and terminal equipment, MCU verification method, can solve the problems of high chip complexity and difficult verification work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

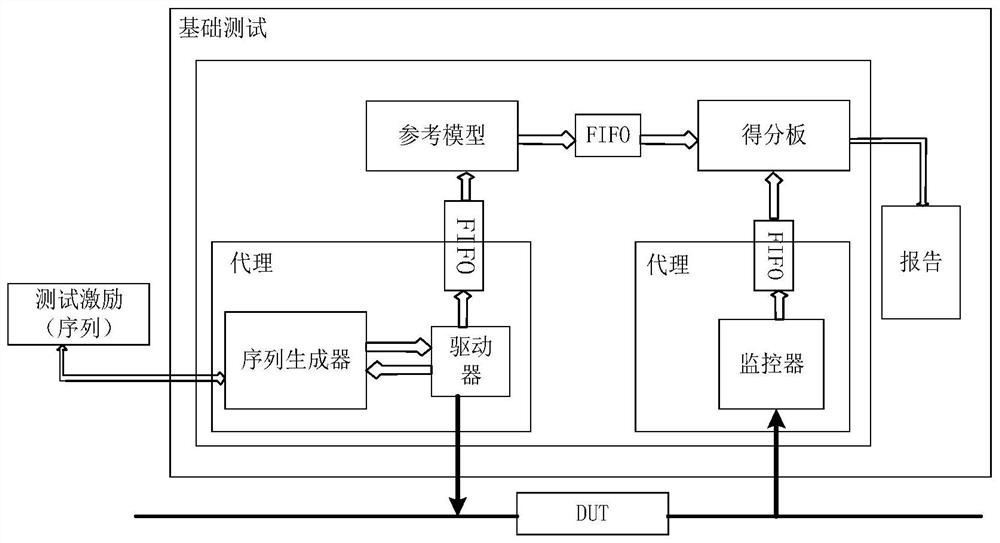

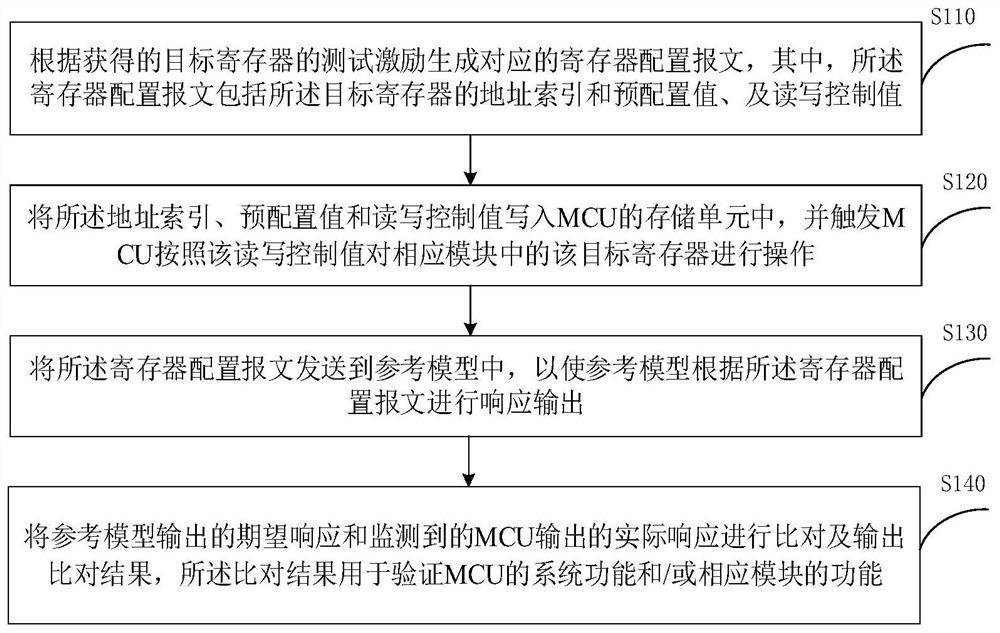

[0057] Please refer to figure 2 , this embodiment proposes an MCU verification method, which can be applied to a general verification platform. When the MCU needs to be verified, a connection between the MCU to be verified and the built general verification platform can be established, so that the general verification platform can be used to communicate with the MCU. interactively to verify that the MCU is functioning properly. In this embodiment, simulation verification will be performed based on the UVM verification platform.

[0058] see figure 2 A UVM verification platform architecture shown, exemplary, the UVM verification platform architecture may include a sequencer (sequencer), a driver (driver), a monitor (monitor), a scoreboard (scoreboard), an agent (agent) and Reference model (reference model) and other components, specifically through the transaction level to build the actual required verification platform. Such as figure 2 As shown, the sequencer is connec...

Embodiment 2

[0092] Please refer to Figure 7 , based on the method of the above-mentioned embodiment 1, this embodiment proposes an MCU verification system. Exemplarily, the MCU verification system includes an MCU to be verified and a general verification platform, and the general verification platform is connected to the MCU to be verified, wherein the general verification The platform is also built with the same reference model as the MCU function to be verified. In this embodiment, the universal verification platform can adopt the UVM verification platform in the first embodiment above.

[0093] Exemplarily, as figure 2As shown, the UVM verification platform mainly includes components such as a sequencer, a driver, a monitor, and a score board. The driver and the monitor are respectively connected to the MCU to be verified through a physical interface, and the sequencer is connected to the driver. The score boards are respectively connected through FIFO in turn, and the monitor is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More