High-linearity phase interpolation circuit

A phase interpolation and high linearity technology, applied in the direction of single output arrangement, etc., can solve the problem of sacrificing chip area and power consumption, achieve the effect of sacrificing area and power consumption, benefiting layout realization, and avoiding the difficulty of realization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

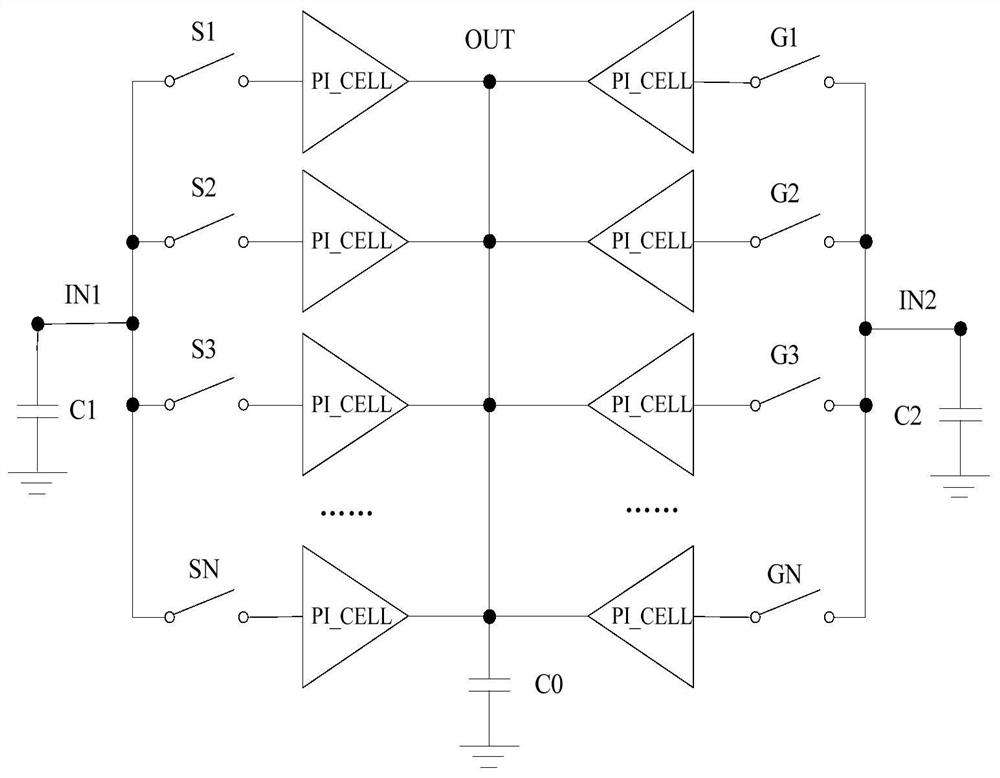

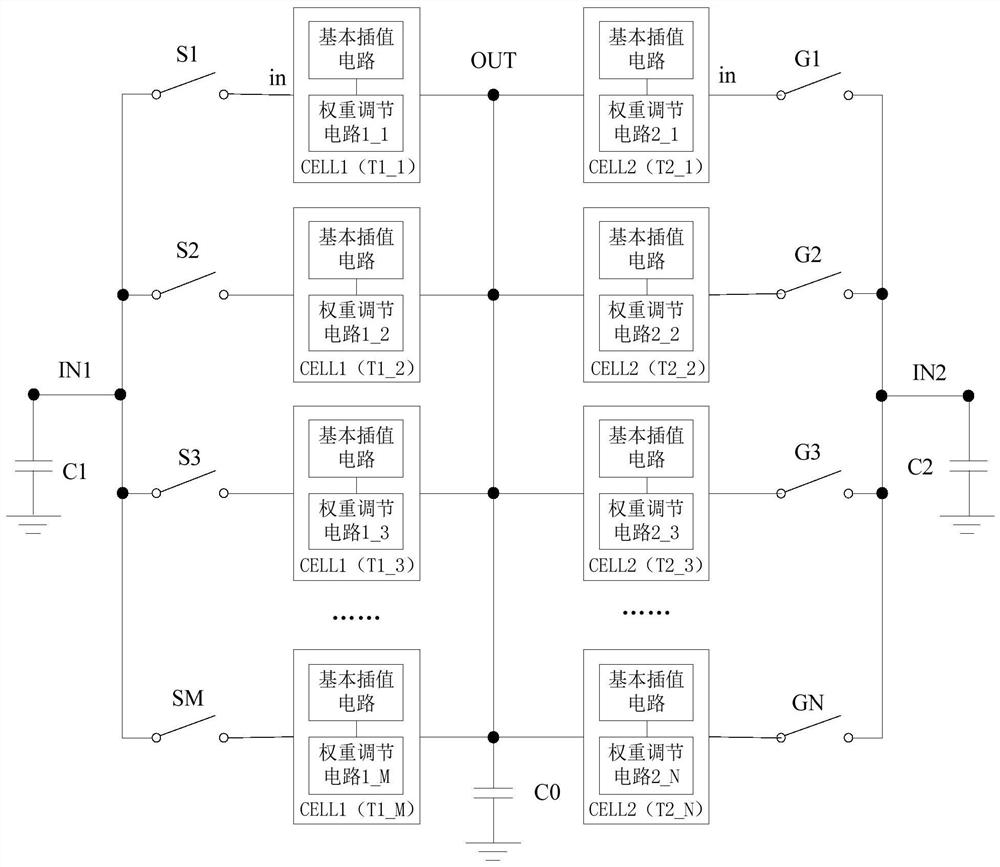

[0033]The present application discloses a phase interpolation circuit with high linearity. The phase interpolation circuit includes a first parallel circuit composed of M phase interpolation units and a second parallel circuit composed of N phase interpolation units. The input of each phase interpolation unit The terminal in is connected to the input terminal of the parallel circuit, and the output terminal is connected to the output terminal of the parallel circuit. Such as figure 1 As shown, the input terminal of the first parallel circuit is connected to the first clock input terminal IN1 and grounded through the first capacitor C1, and the output terminal of the first parallel circuit is connected to the clock output terminal OUT. The input terminal of the second parallel circuit is connected to the second clock input terminal IN2 and g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More