Semiconductor structure with micro-channel, chip stacking structure and preparation method

A chip stacking and semiconductor technology, which is applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of high difficulty and complexity in preparation, reduce the difficulty and complexity of preparation, and simplify the preparation method. Effect of Surface Cleanliness and Planarity Requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

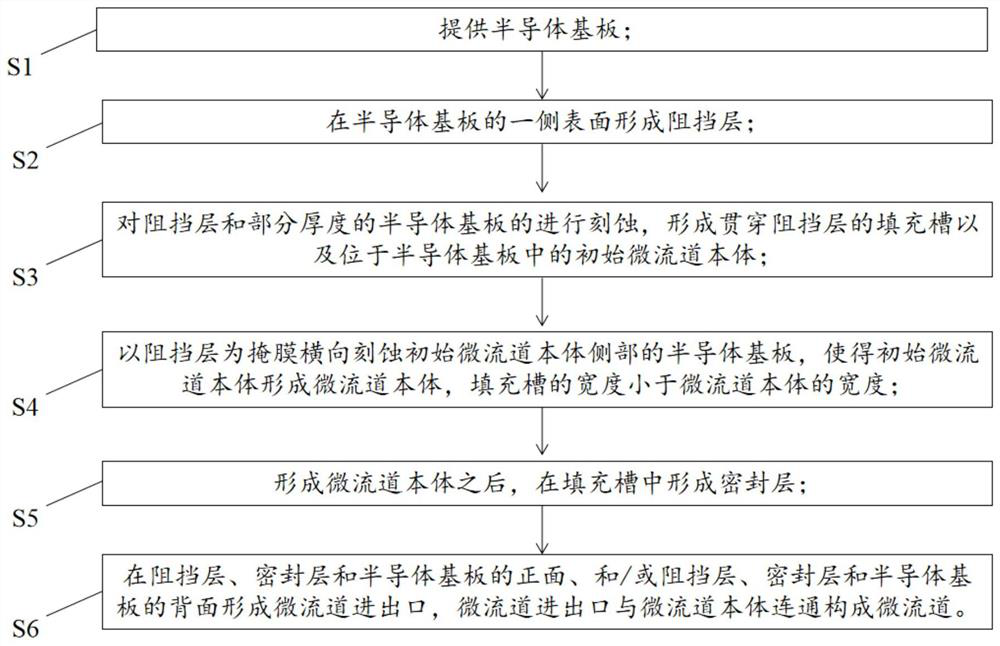

[0050] see figure 1 , the present embodiment provides a method for preparing a semiconductor structure with a microchannel, comprising the following steps:

[0051] S1. Provide semiconductor substrates;

[0052] S2, forming a barrier layer on one side surface of the semiconductor substrate;

[0053] S3. Etching the barrier layer and part of the thickness of the semiconductor substrate to form a filling groove penetrating through the barrier layer and an initial microchannel body located in the semiconductor substrate;

[0054] S4, using the barrier layer as a mask to laterally etch the semiconductor substrate on the side of the initial microchannel body, so that the initial microchannel body forms a microchannel body, and the width of the filling groove is smaller than that of the microchannel the width of the body;

[0055] S5, after forming the micro-channel body, forming a sealing layer in the filling groove;

[0056] S6, forming a micro-channel inlet and outlet on the ...

Embodiment 2

[0088] This embodiment provides a method for preparing a stacked chip structure, including: forming a semiconductor structure. The method for forming the semiconductor structure adopts the method for preparing a semiconductor structure with micro-channels provided in Embodiment 1. The method for manufacturing the stacked chip structure has all the advantages of the method for manufacturing the semiconductor structure, and will not be repeated here.

[0089] As an optional implementation, the semiconductor structure is an adapter board; see Figure 12-Figure 13 , the preparation method of the chip stack structure further includes: providing a substrate 11; setting the adapter plate on the substrate 11, the adapter plate is electrically connected to the substrate 11; setting the adapter plate on the adapter plate The second chip 12 is electrically connected to the adapter board. The substrate 11 can be an organic substrate or a ceramic substrate.

[0090] Specifically, see F...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More