Visual computer-aided chip design and simulation verification method and system

A computer-aided, simulation verification technology, applied in computer-aided design, calculation, special data processing applications, etc., can solve the problems of slow calculation speed, incomplete simulation, slow circuit simulation speed, etc., to improve accuracy and improve simulation verification Speed, the effect of ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

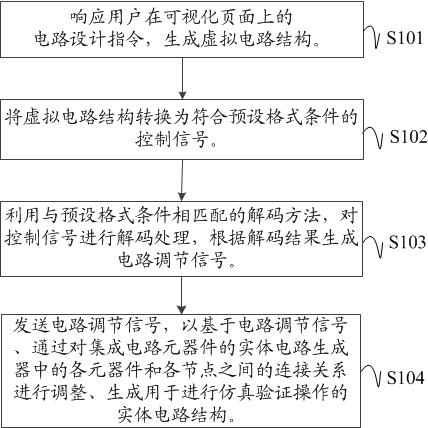

Image

Examples

Embodiment Construction

[0054] In order to enable those skilled in the art to better understand the solution of the present invention, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0055] The terms "first", "second", "third", and "fourth" in the specification and claims of this application and the above drawings are used to distinguish different objects, rather than to describe specific order. Furthermore, the terms "comprising" and "having", and any variations thereof, are intended to cover a non-exclusive inclusion. For example, a process, method, system, product, or device comprisin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More