FPGA layout and wiring method with soft error sensing

A technology of placement and routing, soft error, applied in the field of FPGA placement and routing of soft error perception, can solve problems such as prominent irradiation problem, and achieve the effect of solving low operation efficiency, improving parallelism, and improving robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be further elaborated below in conjunction with embodiment.

[0049] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

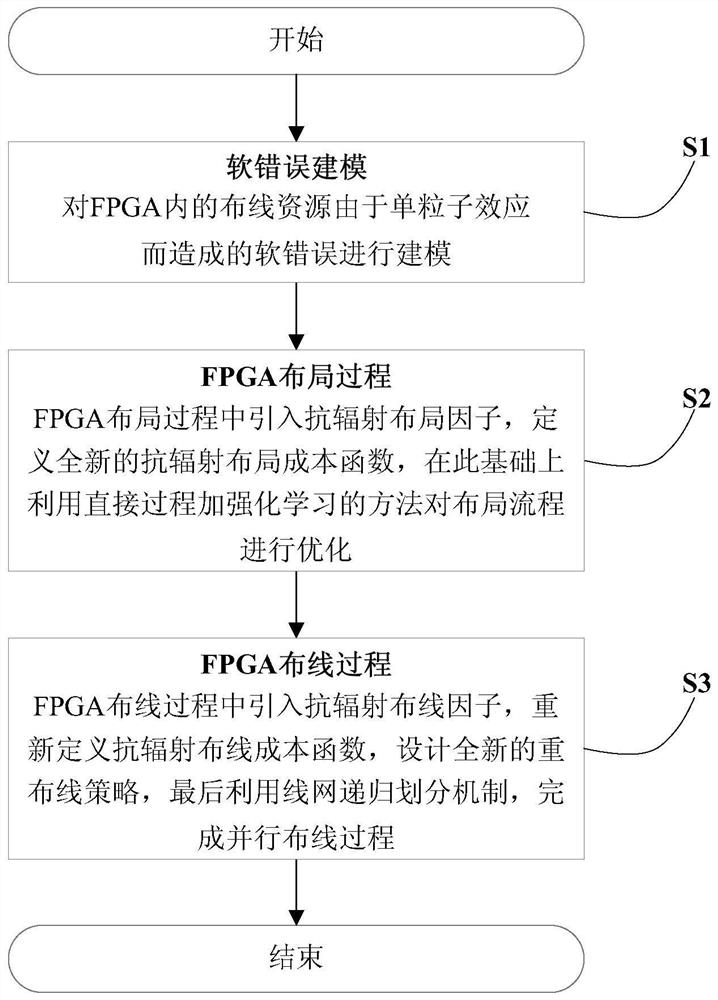

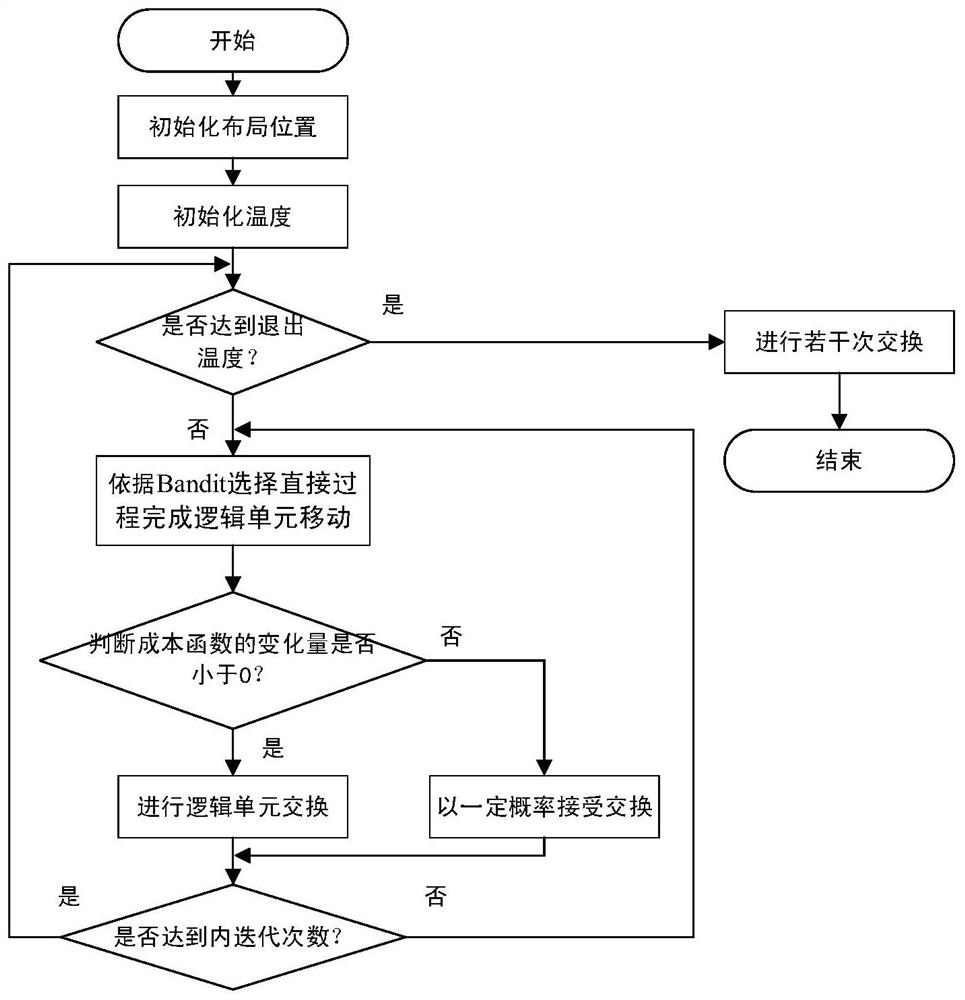

[0050] The idea of the present invention is as figure 1 As shown: Step S1, firstly, analyze and model the soft errors caused by the single event effect in the routing resources in the FPGA; Step S2, introduce the radiation-resistant layout factor in the FPGA layout process, and define the radiation-resistant layout cost function, here On the basis of using the me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More