Method for optimizing via hole anti-pad wiring, circuit board, equipment and storage medium

A technology of anti-pad and printed circuit board, which is applied in the direction of printed circuit, printed circuit manufacturing, printed circuit components, etc., can solve the problems of complex board manufacturing process, failure to meet design requirements, increase cost, etc., to improve the chain The continuity of road impedance, the optimization of via impedance, and the effect of reducing signal reflection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

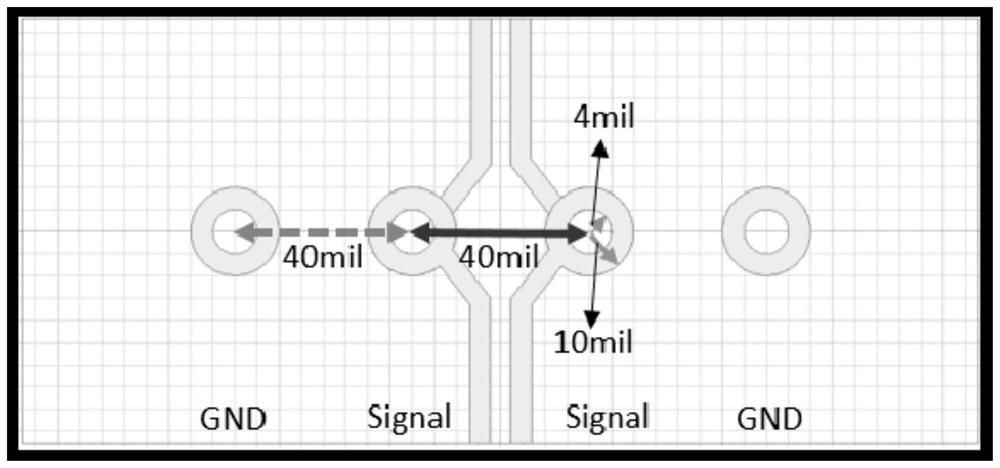

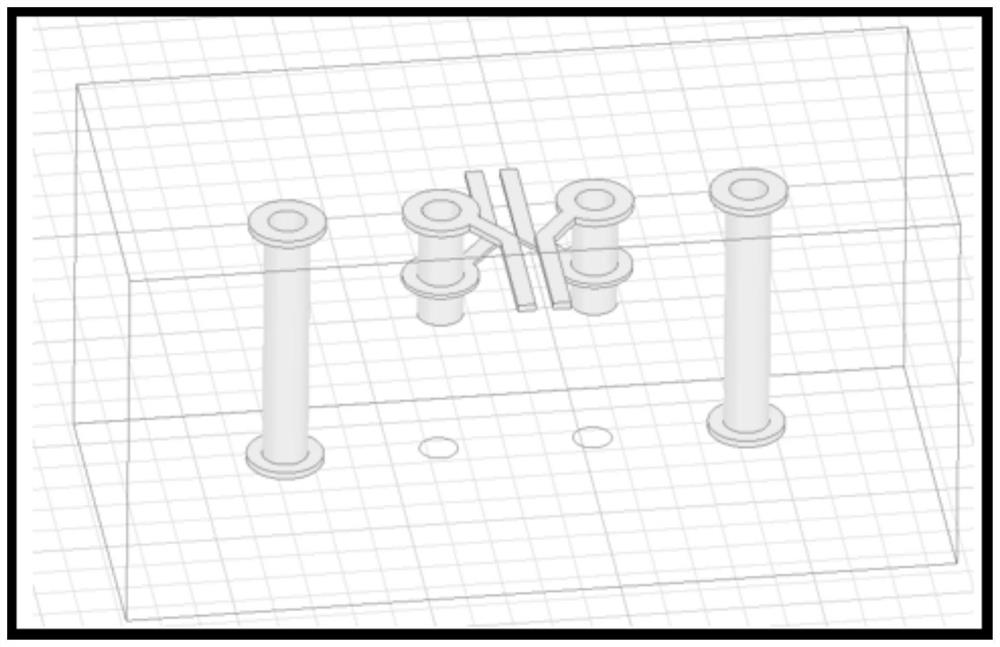

[0036] In order to further illustrate the design method of the present invention, a specific via is taken as an example to describe in detail, as figure 1 The via design of a PCIe Gen4 link is given, in which the radius of the signal hole is 4mil, and the radius of the via pad (via pad) is 10mil. The signal traces on the via hole are changed from layer L1 to layer L5. Such as figure 2 A three-dimensional diagram of the via design of a PCIe Gen4 link in China is given. The target controlled impedance of the vias is 85ohm±2ohm.

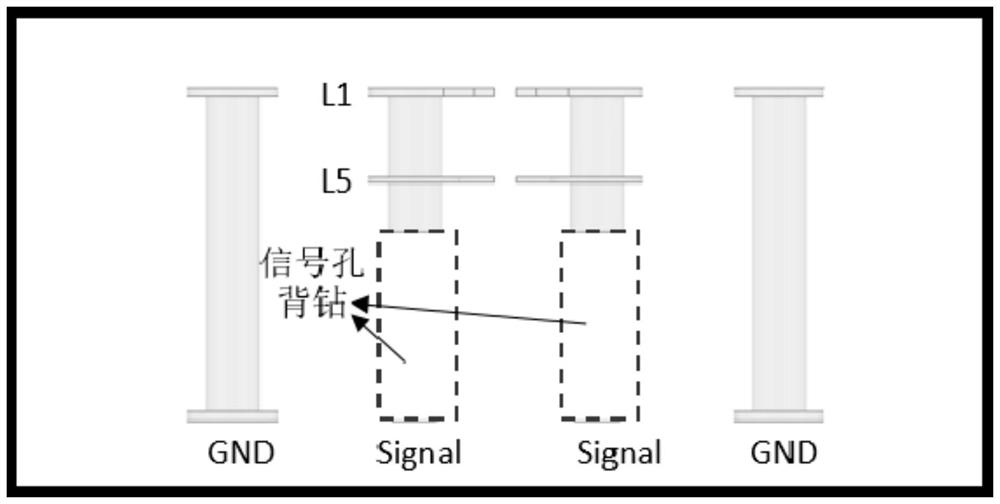

[0037]Due to the high signal rate, the via hole has a 51mil via stub (via stub), so the signal hole is back-drilled, and the back-drilling depth is 41mil, such as image 3 The back-drilling of the vias is given, and only the back-drilling is performed for the signal holes. Figure 4 It shows the Antipad design situation of the via hole, set the Antipad radius as the variable Antipad, take 15mil as the initial value, and use 5mil as the step size to...

Embodiment 2

[0084] Based on the method for optimizing via anti-pad wiring provided in Embodiment 1 of the present invention, Embodiment 2 of the present invention proposes a printed circuit board. The printed circuit board is processed by optimizing the routing of the anti-pad of the via hole; the method of making the printed circuit board is: for the anti-pad of the via hole of different sizes, the first value of the first distance is used as the initial value, and the second The numerical value is the step size for traversal, and the first distance corresponding to the minimum impedance of the via is determined; the first distance is the straight-line distance between the differential line coupling position in the anti-pad of the via and the middle of the differential signal hole.

[0085] The first value is 0mil or the radius of the via anti-pad. When the first value is 0mil, the second value is any value greater than 0 and less than the radius of the via anti-pad; when the first value...

Embodiment 3

[0098] Based on the method for optimizing via anti-pad routing proposed in Embodiment 1 of the present invention, Embodiment 3 of the present invention proposes a via-anti-pad routing optimization device for printed circuit boards, including:

[0099] The memory is used for storing the computer program; the processor is used for implementing the method steps of optimizing the routing of the via hole anti-pad when executing the computer program. The process of the method is:

[0100] For via anti-pads of different sizes, the first value of the first distance is used as the initial value, and the second value is used as the step size to traverse to determine the first distance corresponding to the minimum via hole impedance; the first distance is the over The linear distance between the differential line coupling position in the anti-pad of the hole and the middle of the differential signal hole.

[0101] The first value is 0mil or the radius of the via anti-pad. When the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More