Phase-locked loop circuit reference stray elimination method, elimination device and phase-locked loop system

A phase-locked loop and circuit technology, applied in the field of circuits, can solve problems such as failure, improvement of reference stray elimination effect, difficulty in obtaining definite and quantitative effects, etc., to achieve the effect of expanding the frequency band bandwidth and improving the elimination effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

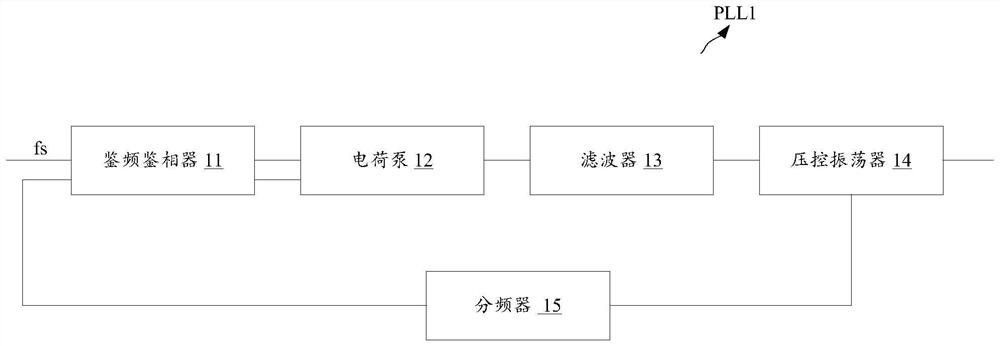

[0058] Such as figure 1 The schematic diagram of the structure of the charge pump phase-locked loop circuit shown, the phase-locked loop PLL1 includes a frequency detector 11, a charge pump 12, a filter 13, a voltage-controlled oscillator 14 and a frequency divider 15, wherein, by the voltage The controlled oscillator 14 generates a clock signal, and after the frequency division by the frequency divider 15, the frequency division signal is obtained and fed back to the frequency and phase detector 11, and the frequency division signal and the reference signal are divided by the frequency and phase detector 11 The frequency fs and the phase are compared, and the comparison result is filtered by the charge pump 12 and the filter 13 and then output to the voltage-controlled oscillator 14 for frequency control.

[0059] The key performance parameters of the phase-locked loop include phase noise, unwanted by-products or spurious frequencies in the frequency synthesis process (referr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com