Laser marking method of silicon wafer and manufacturing method of heterojunction cell

A laser marking method and technology for heterojunction cells, which are used in photovoltaic power generation, manufacturing tools, laser welding equipment, etc., can solve the problems of silicon wafer damage and affect the performance of heterojunction cells, and achieve good electrical performance and battery conversion High efficiency and reduce mechanical damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

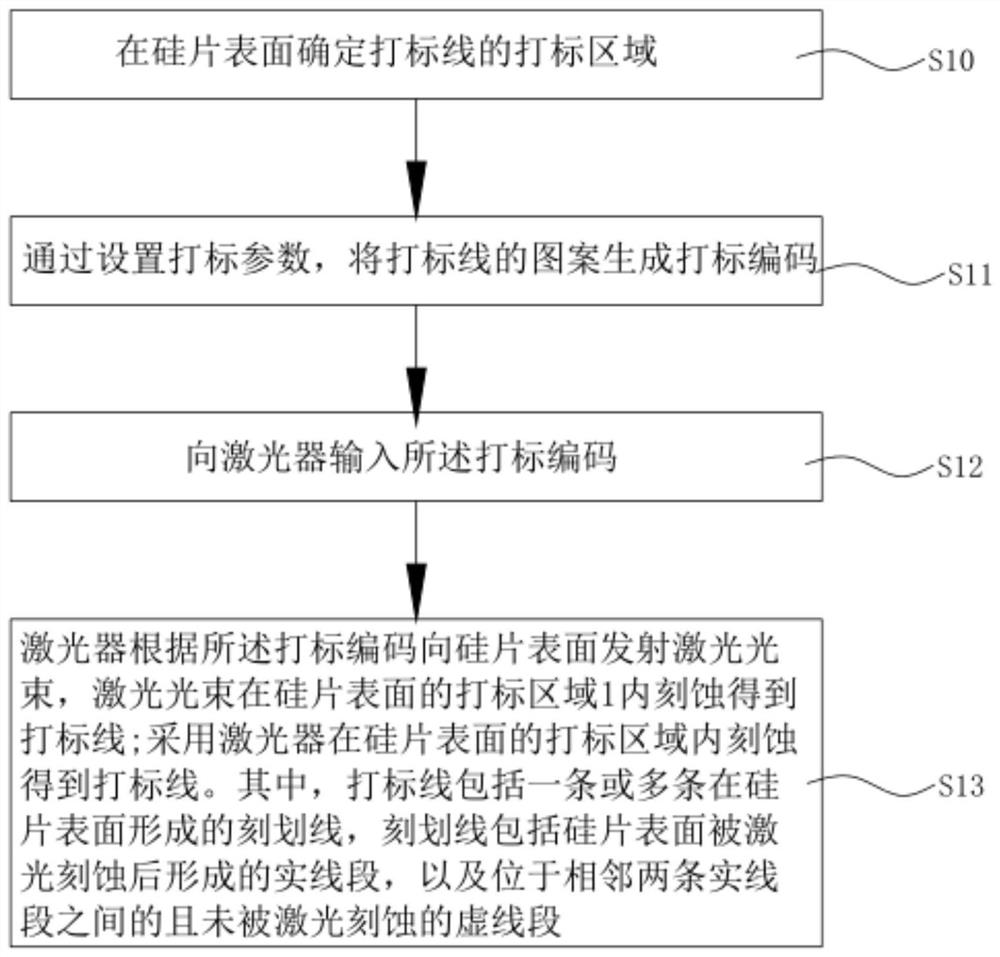

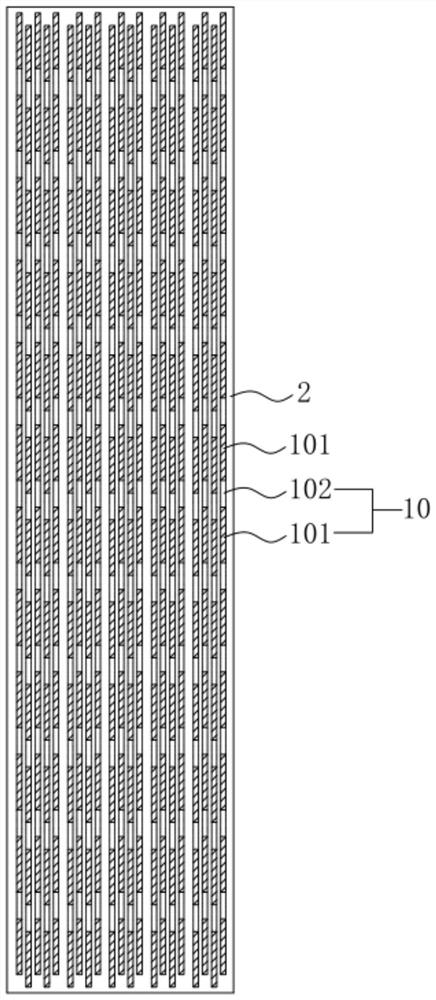

[0044]A silicon wafer laser marking method is exemplified by combining the silicon wafer laser marking method with the application of silicon wafers in the manufacture of heterojunction cells. combine figure 1 As shown in -2, a laser marking method for a silicon wafer includes the following steps:

[0045] Step S10: Determine the marking area 1 of the marking line on the surface of the silicon wafer 2.

[0046] Specifically, when determining the marking area 1, the marking line should be located as far as possible under the auxiliary gate line 4 after the silicon wafer 2 is made into a heterojunction cell, avoiding the position of the main grid line 3; and the size of the marking area 1 is 5mm2-30mm 2 , the distance between the marking line in the marking area 1 and the edge of the silicon wafer 2 is kept between 1mm-3mm. Marking area 1 is as close to the edge of silicon wafer 2 as possible to reduce the influence of laser marking on grid lines during screen printing, other...

Embodiment 2

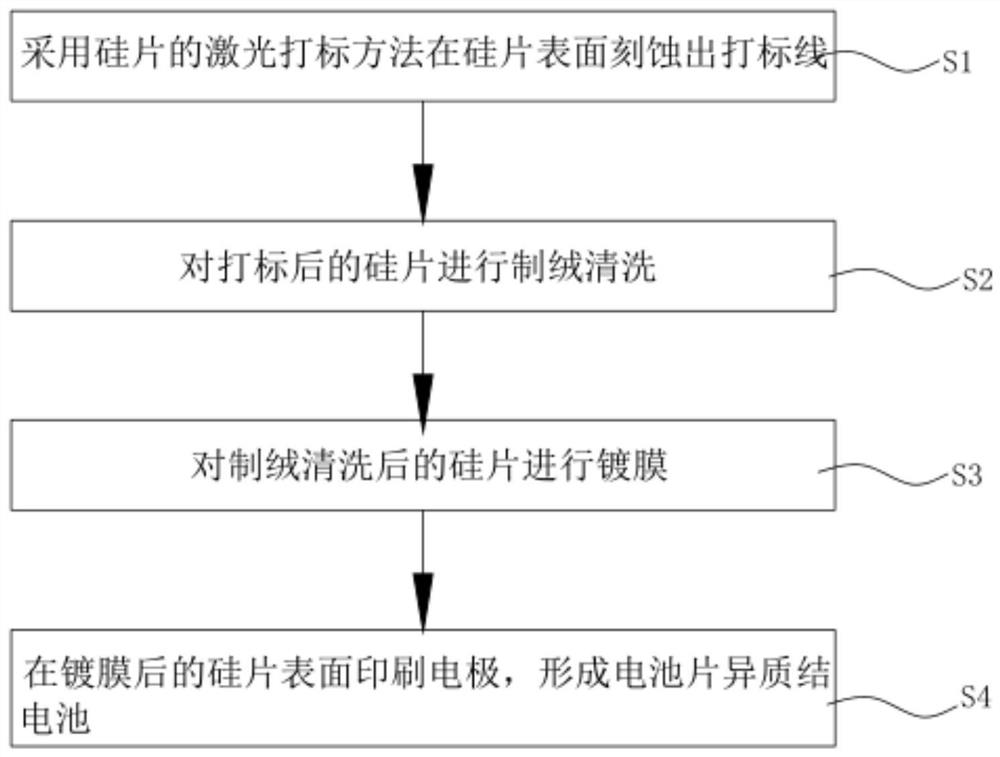

[0059] combine image 3 and Figure 4 As shown, Embodiment 2 of the present invention provides a method for manufacturing a heterojunction battery, including the following steps:

[0060] Step S1, using the laser marking method for silicon wafers in the above-mentioned embodiment 1 to etch a marking line on the surface of the silicon wafer; Step S2, performing texturing cleaning on the marked silicon wafer 2; Step S3, cleaning the texturing The finished silicon wafer 2 is coated; step S4, printing electrodes on the surface of the coated silicon wafer 2 to form a heterojunction cell.

[0061] In this embodiment, the fabricated heterojunction battery is a silicon-based heterojunction heterojunction battery, and the coating process includes a PECVD coating process and an ITO film coating process performed in sequence. When the heterojunction heterojunction cell uses the N side as the light incident surface, the marking line needs to be marked on the N side; when the heterojunct...

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More