LDMOS transistor and preparation method thereof

A transistor and semiconductor technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of conflicting on-resistance performance requirements, high breakdown voltage and low breakdown voltage, etc., to improve the breakdown voltage BV, reduce the conduction On-resistance, the effect of improving the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

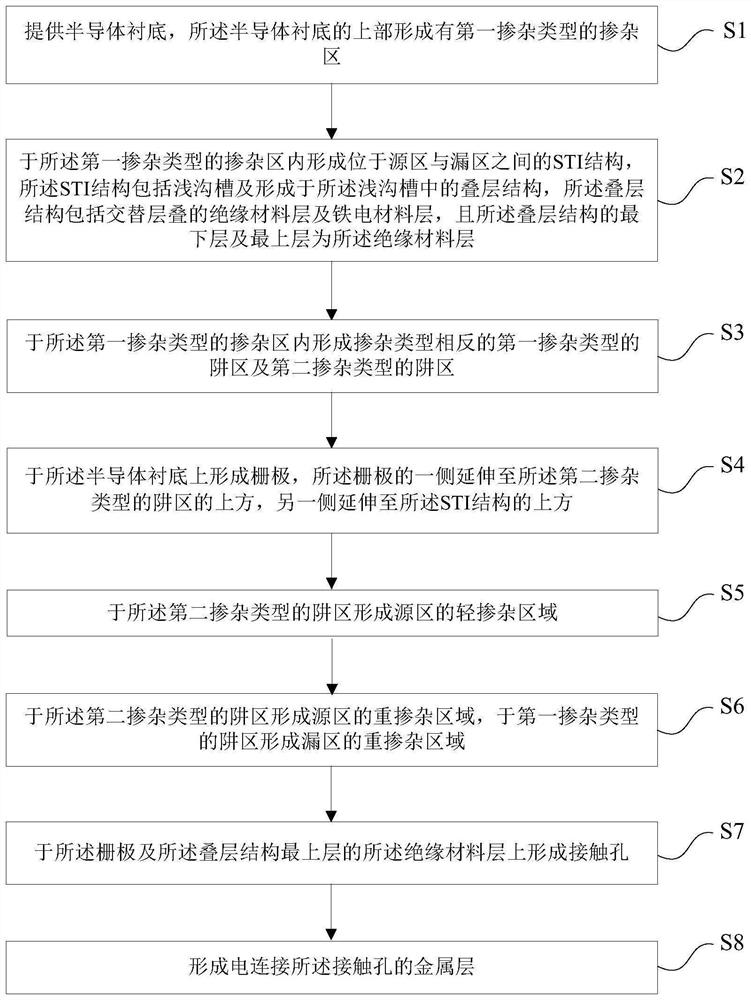

[0069] This embodiment provides a method for preparing an LDMOS transistor. For ease of understanding, this embodiment is described by taking the method for preparing an N-type LDMOS transistor as an example. Those skilled in the art can change the doping type of the transistor as needed to obtain A method for preparing a P-type LDMOS transistor with the same structure.

[0070] Taking the N-type LDMOS transistor as an example, a capacitor structure is formed between the gate and the drain by setting a contact hole and a metal layer between the gate and the STI structure. When the transistor is in the on state, the gate voltage is high, Additional electrons can be induced under the insulating material layer (LDMOS drift region) in the STI structure, thereby reducing the on-resistance Ron, and when the transistor is in the off state, the gate voltage is grounded, and the contact hole will be in the STI structure. An additional depletion region is induced under the insulating ma...

Embodiment 2

[0094] This embodiment provides an LDMOS transistor. The LDMOS transistor can be prepared by the preparation method of the first embodiment above, but is not limited to the preparation method described in the first embodiment, as long as the LDMOS transistor can be formed. For the beneficial effects achieved by the LDMOS transistor, please refer to Embodiment 1, and details will not be repeated below. In addition, the following embodiments are described by taking an N-type LDMOS transistor as an example, and those skilled in the art can change the doping type of the transistor as required to obtain a P-type LDMOS transistor with the same structure.

[0095] Such as Figure 11 shown, the LDMOS transistor consists of:

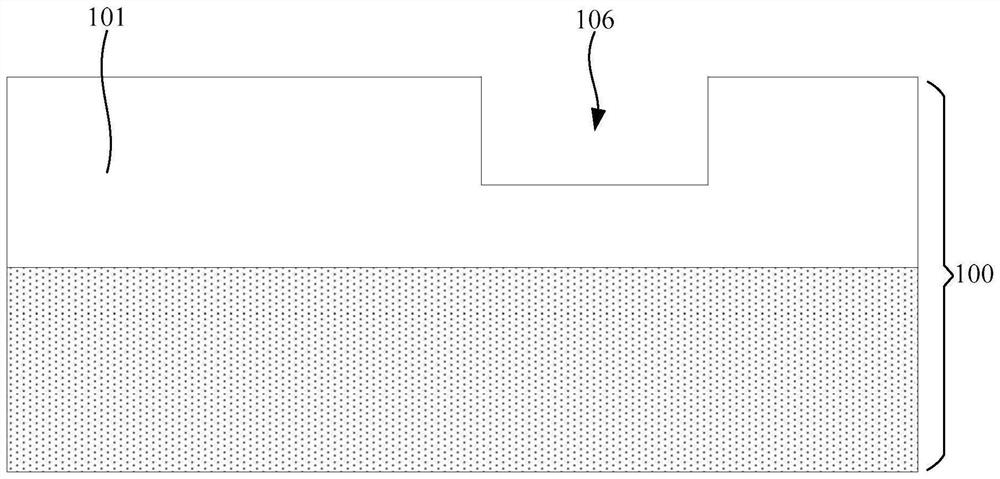

[0096] A semiconductor substrate 100, an N-type doped region 101 is formed on the upper part of the semiconductor substrate 100, and an N-type well region 102 and a P-type well region 103 with opposite doping types are formed in the N-type doped region 101;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More