Memory-limited digital circuit parallel static learning method and system

A technology of digital circuits and learning methods, applied in the field of data processing, to achieve the effect of improving effective utilization, avoiding memory, and improving running speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

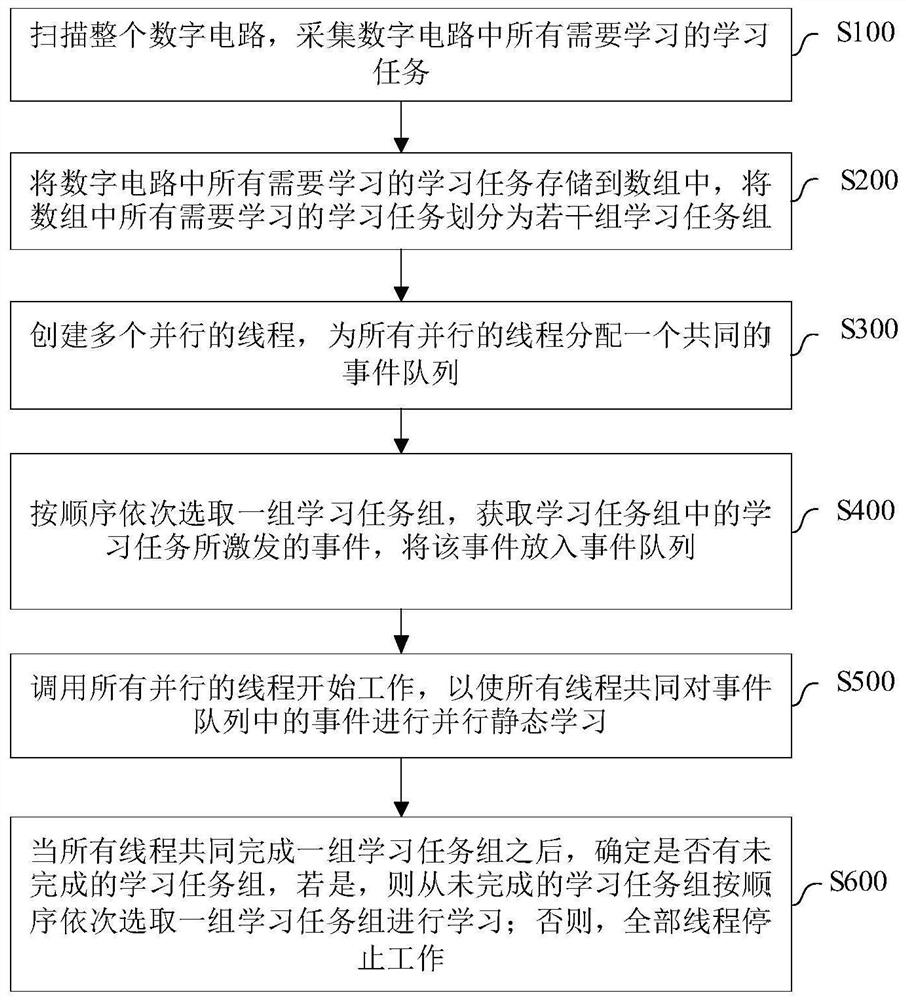

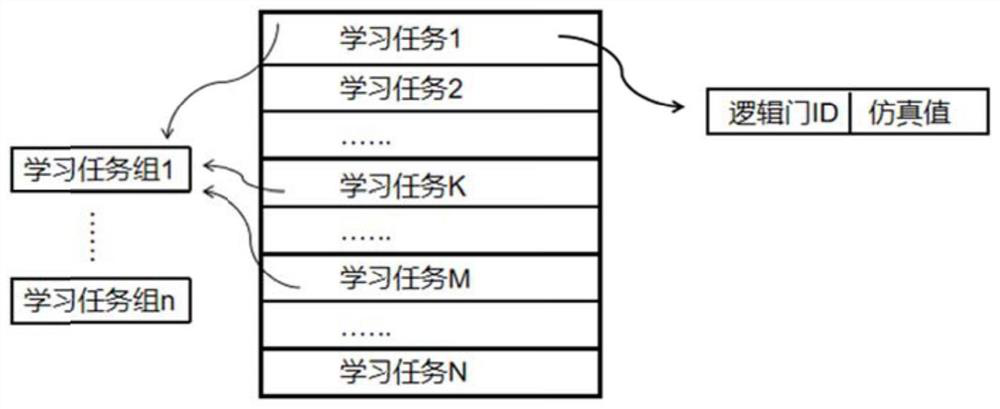

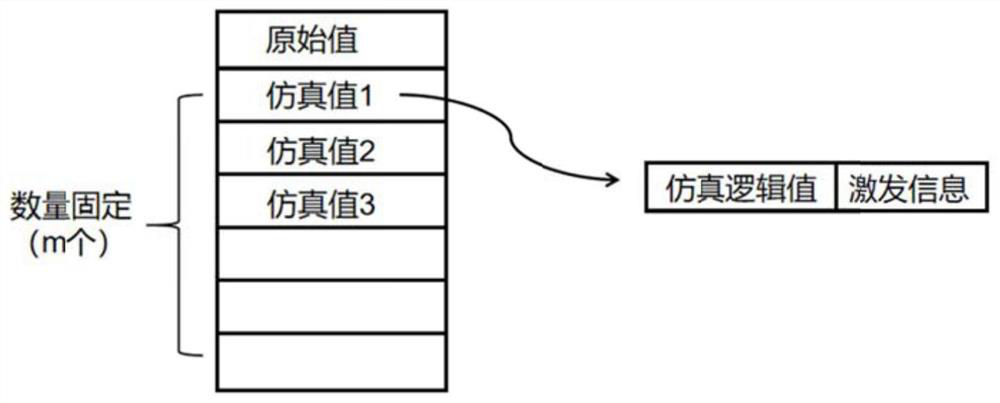

Method used

Image

Examples

Embodiment Construction

[0051] The concept, specific structure and technical effects of the present application will be clearly and completely described below in conjunction with the embodiments and drawings, so as to fully understand the purpose, scheme and effect of the present application. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0052] When the inventor was conducting research on static learning, he found that the existing single-thread implementation had the problem of too long running time. In response to this problem, the inventor extracted the place that can be implemented in parallel in the static learning process, and proposed a new parallel implementation method for static learning based on the premise of limited memory, which can not only avoid consuming a large amount of memory, but also greatly improve static learning. The speed at which learning runs.

[0053] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More