FPGA (Field Programmable Gate Array) hardware architecture, data processing method thereof and storage medium

A technology of hardware architecture and data processing, applied in the fields of computer equipment and storage media, FPGA hardware architecture and data processing, it can solve the problems of complex software settings, and achieve the effect of simplifying hardware design, resource realization, and simplifying hardware settings.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

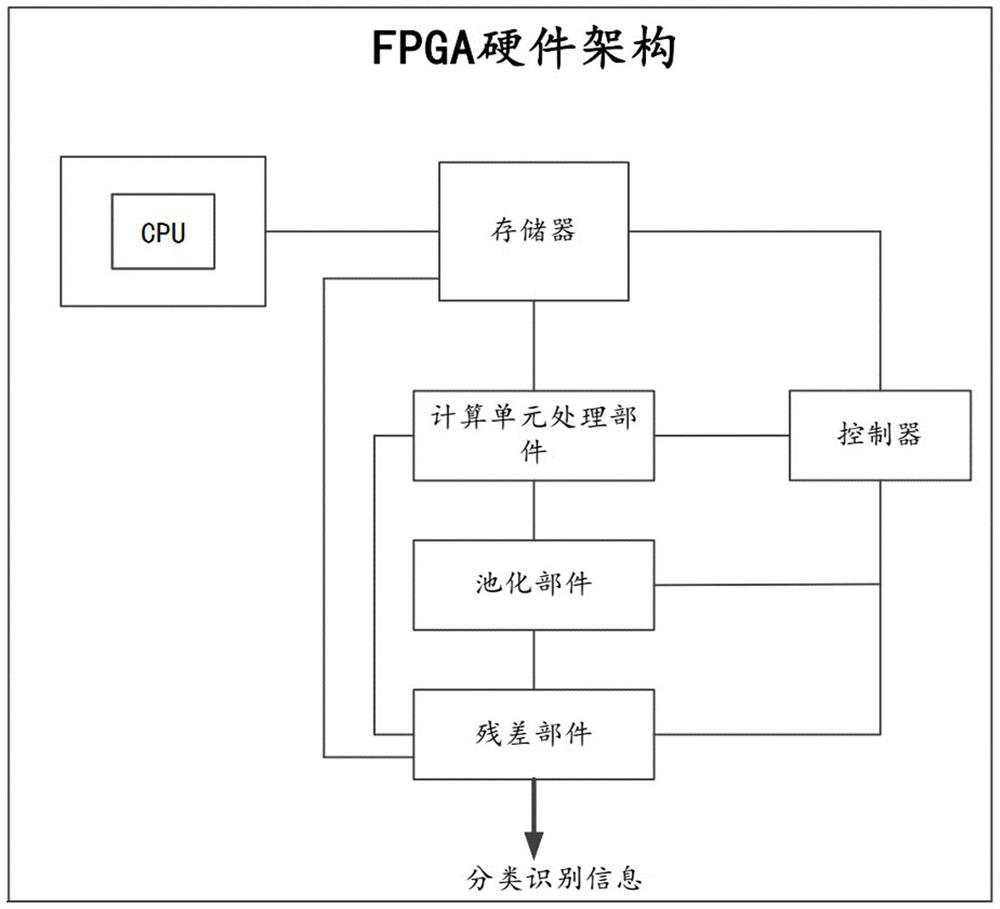

[0034] A kind of data processing method that this application provides is applied to FPGA hardware framework, can be applied to such as figure 1 shown in the FPGA hardware architecture. Among them, such as figure 1 As shown, the FPGA hardware architecture includes a central processing unit, a memory, a computing unit processing unit, a pooling unit, a residual unit, and a controller. The central processing unit is connected to the memory, and when receiving the first picture characteristic data to be processed, stores the first picture characteristic data in the memory. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More