Parasitic capacitance test structure and method of FinFET

A technology for testing structure and parasitic capacitance, which is applied in semiconductor/solid-state device testing/measurement, circuits, electrical components, etc. It can solve problems such as unfavorable mass production, undetectable M0 parasitic capacitance value, metal gate butterfly depression, etc., to achieve Ease of mass production and calculation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

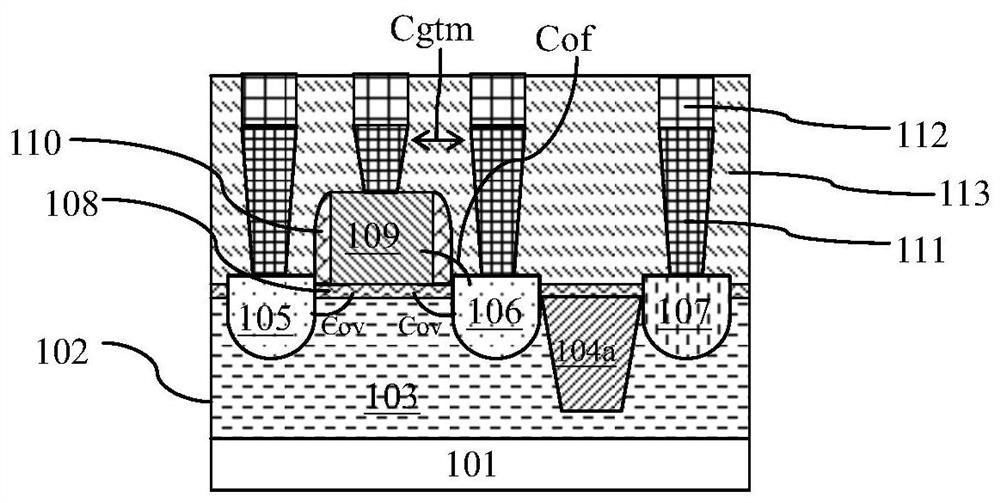

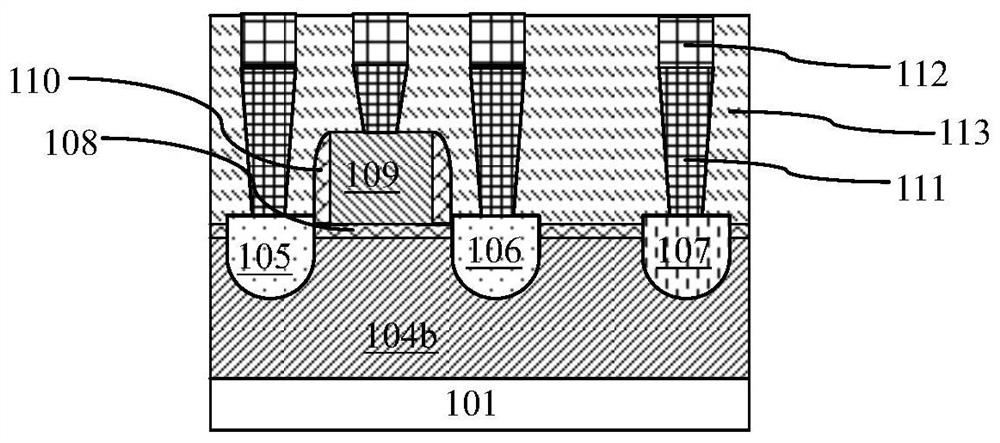

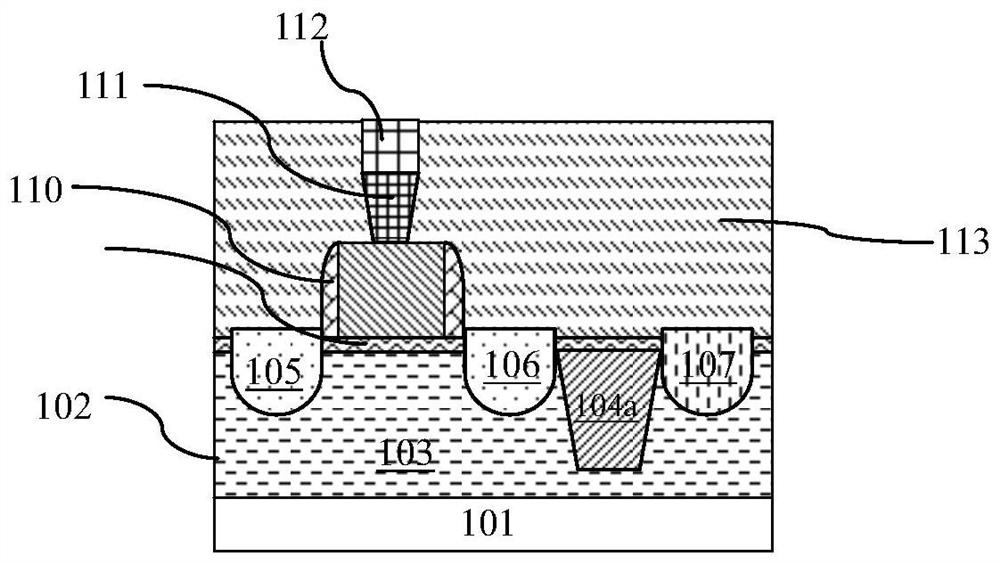

[0066] Such as image 3 As shown, it is a schematic structural diagram of the FinFET in the embodiment of the present invention; in the parasitic capacitance test structure of the FinFET in the embodiment of the present invention, the FinFET 301 includes a gate structure, a lightly doped source region composed of a lightly doped region of the first conductivity type and Shallowly doped drain region, sidewall 210, source region 205 and drain region 206 composed of heavily doped region of the first conductivity type, well region 203 of second conductivity type and body lead-out region composed of heavily doped region of the second conductivity type District 207.

[0067] The gate structure is formed by stacking a gate dielectric layer 208 and a gate conductive material layer 209 .

[0068] The second conductivity type well region 203 is formed in the fin body 202 . In the embodiment of the present invention, the fin body 202 is formed by patterning and etching a semiconductor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More