Multi-chip fan-out type packaging method and packaging structure

A packaging method and a fan-out technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of not being able to fully reflect the advantages of thin packaging, increase the thickness of the package, and reduce the purchase of machines , Reduce production costs and improve economic benefits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0040] As shown in Figure 2, a multi-chip fan-out packaging method in this embodiment includes the following steps:

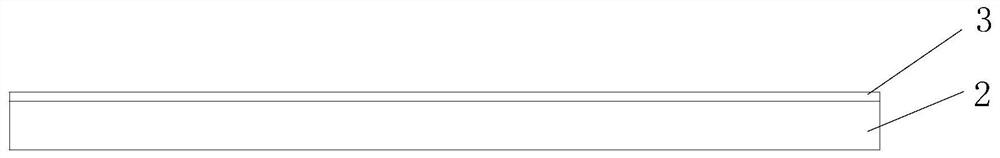

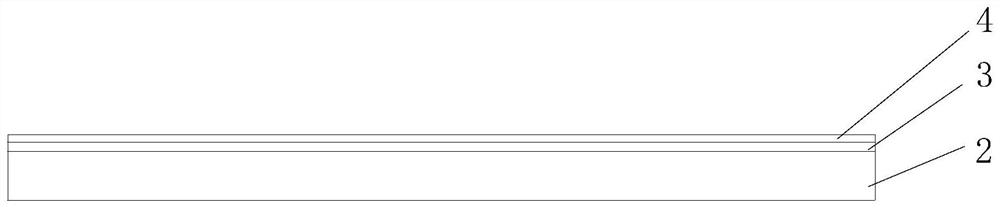

[0041] Step 1, see Figure 2a with Figure 2b As shown, a composite separation layer 3 is coated on the surface of the transparent carrier 2, and then a metal layer 4 with a certain thickness is sputtered on the composite separation layer 3;

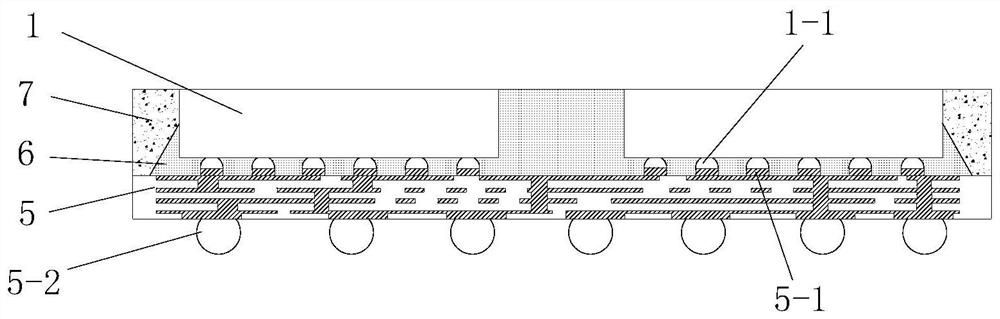

[0042] Step two, see Figure 2c As shown, the rewiring metal circuit layer 5 and the corresponding upper layer metal pad 5-1 are formed on the metal layer 4 by multiple photolithography, sputtering and electroplating;

[0043] Step 3, after thinning the chip 1 as a whole to the target thickness, dicing is performed, and then chip pads 1-1 are made on the bottom of each independent chip 1;

[0044] Step 4, see Figure 2d with Figure 2e As shown, a plurality of chips 1 are welded to the upper metal pad 5-1 of the rewiring metal circuit layer 5 through the chip pad 1-1, and the gap between the pads is underfilled to fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More