Chip embedded-type encapsulation structure with reinforcing structure and encapsulation method of same

A technology to strengthen the structure and packaging structure, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problem of increasing the mismatch probability of interconnection spacing and heat dissipation difficulties, which is not conducive to the integrated development of portable electronic equipment, and the thickness of the packaging structure cannot be reduced, etc. Problems, achieve the effect of strengthening strength, realizing miniaturization, and reducing equipment requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

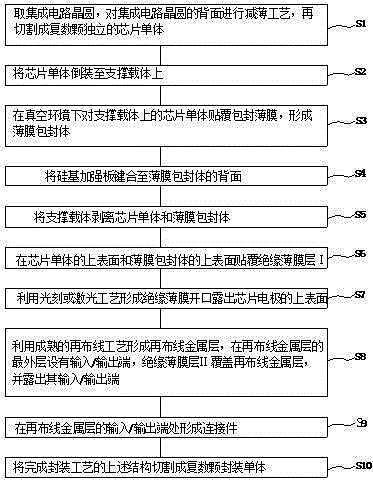

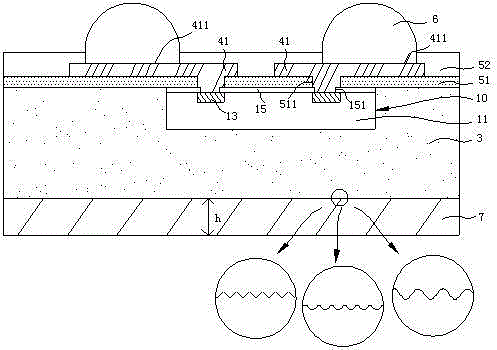

[0075] Embodiment one, see Figure 3A and Figure 3B

[0076] Figure 3A It is a schematic cross-sectional view of Embodiment 1 of a chip-embedded packaging structure with a reinforced structure in the present invention. The chip-embedded packaging structure of the present invention includes a chip unit 10 with a film encapsulation body 3 embedded in the back, and the chip unit 10 The upper surface of the chip body 11 is provided with a chip electrode 13 and its corresponding circuit layout, the chip surface passivation layer 15 covers the upper surface of the chip body 11 and has a chip surface passivation layer opening 151, and the upper surface of the chip electrode 13 exposes the chip The surface passivation layer opens 151 . The material of the film envelope 3 includes but is not limited to epoxy molding compound, which is generally made of high-performance phenolic resin as a curing agent, silicon micropowder as a filler, and various additives. It is in a molten stat...

Embodiment 2

[0095] Embodiment two, see Figure 5A and Figure 5B

[0096] The number of chip monomers can be more than one, and more chip packages with different functions can be realized by adopting chip packaging system collaborative design.

[0097] Figure 5AIt is a schematic cross-sectional view of Embodiment 2 of a chip-embedded packaging structure with a reinforced structure of the present invention. The chip-embedded packaging structure of the present invention includes two chip units 10 and a chip unit whose backs are embedded in a film encapsulation body 3 20, its upper surface is generally arranged flush. The material of the film envelope 3 includes but is not limited to epoxy molding compound, which is generally made of high-performance phenolic resin as a curing agent, silicon micropowder as a filler, and various additives. It is in a molten state at 185°C, and tightly wraps the front, rear, left, and right sides and the back of the chip unit 10. After cooling, it will gr...

Embodiment 3

[0101] Embodiment three, see Figure 6

[0102] The packaging structure of Embodiment 3 is similar to that of Embodiment 1 and Embodiment 2, the difference is that the rewiring metal layer 41 can also be two or more layers to form a plurality of rewiring process layers, so as to realize a multi-layer fan-out packaging structure ,Such as Figure 6 shown. The multi-layer rewiring process layer is an example of three layers, including a rewiring metal layer 41, a rewiring metal layer 43, and a rewiring metal layer 45 to meet the multi-information communication. The wiring process layers are matched, and they are respectively arranged in it to play the roles of insulation, protection, reinforcement, etc. The insulating film layer II 52 is generally made of polymeric organic insulating materials such as epoxy resin and polyimide. The outermost layer of the multi-layer redistribution process layer is provided with input / output terminals, and the number of input / output terminals ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More