Integrated circuit mask layout, pattern correction method and mask thereof

An integrated circuit and mask technology, applied in the field of integrated circuit mask layout, can solve the problem of inability to obtain a process window, and achieve the effect of a good process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0025] This embodiment provides a layout of an integrated circuit mask. The layout includes the graphics required in various photolithography processes. The improvement of the present invention lies in the relationship between the active area graphics, the sealing ring graphics and the two graphics, and other graphics. It is a prior art, so it will not be repeated in the embodiment.

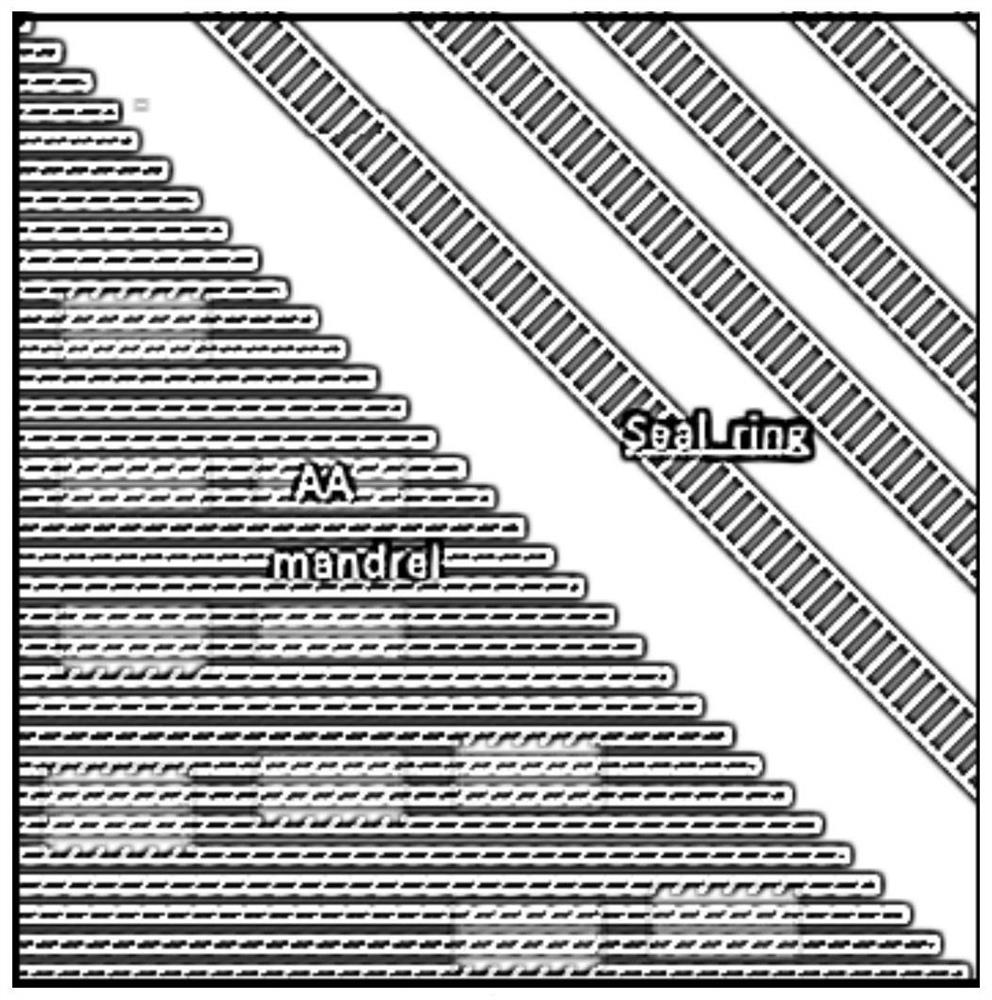

[0026] Such as figure 2 As shown, the integrated circuit mask layout of this embodiment includes a plurality of active region patterns 1 and a plurality of sealing ring patterns 2;

[0027] The active region pattern 1 is parallel to the horizontal direction of the mask layout;

[0028] The sealing ring pattern 2 forms an included angle with the horizontal direction of the mask layout.

[0029] A plurality of active area patterns 1 form a group to form multiple groups of active area patterns;

[0030] Each group of active region patterns corresponds to adjacent alignment marks 3, and the edge ...

Embodiment 2

[0036] This embodiment provides a pattern correction method for an integrated circuit mask layout, and the integrated circuit mask layout is the layout in Embodiment 1.

[0037] Such as figure 2 shown. In this embodiment, the optical proximity effect correction method OPC is used to correct the original pattern of the integrated circuit mask layout, and the edge of each active region pattern 1 in the same group of active region patterns near the seal ring pattern 2 is The vertical direction of the mask layout is flush. Make the floating distance corresponding to each active area pattern 1 and the adjacent alignment mark 3 in the same group of active area patterns the same

Embodiment 3

[0039] This embodiment provides an integrated circuit mask, including the layout of the integrated circuit mask described in Implementation 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com